С повышением степени интеграции микросхем стало возможным реализовать на одном кристалле сложные функциональные блоки. Зa недолгую историю развития элементной базы микропроцессорных вычислительных устройств были разработаны принципиально новые структуры БИС. Такие микросхемы, имеющие высокую степень интеграции и работающие согласно заданной программе, получили название микропроцессорных БИС (МП БИС). Стало возможным реализовать ЭВМ на нескольких типах МП БИС, объединенных в так называемые микропроцессорные комплекты (МПК) БИС, которые отличаются друг от друга функциональными возможностями, технологией изготовления, конструктивными особенностями, быстродействием, потребляемой мощностью и т.п.

Микропроцессорные БИС принято разделять на три основных класса: секционированные с наращиванием разрядности и микропрограммным управлением; модульные МП - на основе однокристальных МП БИС с фиксированным набором команд и разрядностью; однокристальные микроЭВМ.

Секционированные МП БИС включают совместимые микросхемы различного функционального назначения, на основе которых можно реализовать MПC различной структуры и разрядности, кратной разрядности секции. В зависимости от назначения разрабатываемой аппаратуры выбирается структура секционированных БИС и система команд. Эти БИС широко применяются при проектировании высокопроизводительных мультимикропроцессорных систем.

МП БИС на основе однокристальных МП и однокристальных микроЭВМ, обладающие меньшей производительностью, но гибкой системой команд и большими функциональными возможностями, ориентированы на широкое применение в различных областях науки, техники и производства - от контроллеров и калькуляторов, до МПС управления, цифровой обработки сигналов и интеллектуальных робототехнических систем.

В настоящее время наибольшее распространение получили МП БИС на основе разновидностей МОП- технологии и интегральной инжекционной логики(И2Л). Требования к быстродействию предопределили развитие биполярных МП БИС на основе транзисторно-транзисторной логики с диодами Шотки(ТТЛШ) и эмиттерно-связанной логики (ЭСЛ).

Следует отметить, что при проектировании МПС для различных применений обязательным условием эффективного использования МП БИС является конструктивная и технологическая совместимость всей элементной базы системы - микросхем малой, средней и большой степени интеграции, используемых в центральном процессоре, блоках памяти, устройствах ввода-вывода.

Как правило, в состав однокристальных МП БИС, служащих для реализации однокристальных микроЭВМ и МПС на их основе, входят следующие БИС: микропроцессор с памятью, последовательный или параллельный интерфейс, контроллеры (ПДП, прерываний, клавиатуры и т.п.).

В последние годы получила новое развитие номенклатура однокристальных микроЭВМ и специализированных МПК цифровой обработки сигналов, которые имеют большую перспективу применения в силу своих функциональных возможностей и характеристик.

Состав и структура МПК БИС зависят от областей применения и, как правило, имеют минимально необходимое число БИС для организации микроЭВМ и МПС.

Типичным представителем МПС с однокристальным МП является отечественный микропроцессорный комплект серии К1810, в котором реализуются и находят дальнейшее развитие идеи построения одно- и многопроцессорных систем на базе МП БИС с фиксированным набором команд. В комплект входят как универсальные и специализированные процессоры (процессор ввода-вывода, арифметический процессор), так и схемы, позволяющие сформировать магистрали микроЭВМ. Комплект может расширяться за счет разработки новых схем, программно и аппаратно совместимых с МП БИС.

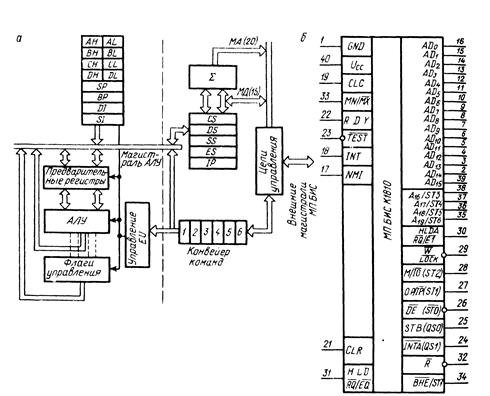

Основной схемой в комплекте является МП БИС К1810ВМ86, которая представляет собой однокристальный 16-разрядный МП с мультиплексной 20-разрядной магистралью адреса и 16-разрядной магистралью данных и рассчитана на работу как в одно-, так и в многопроцессорных системах. Схема выпускается в 40-выводном корпусе (рис. 5.1). Ряд выводов схемы используется для выдачи импульсов управления, синхронизирующих работу микроЭВМ. Питание схемы осуществляется от источника с напряжением 5 В. Синхронизация работы МП БИС осуществляется импульсами внешнего тактового генератора, подаваемыми на вход CLK.

Эффективность работы МП БИС К1810ВМ86 существенно повышена за счет введения команд математических операций (включающих умножение и деление) над 8- и 16-разрядными числами, команд побитовой обработки чисел, команд работы с массивами данных, расширения видов прерываний работы МП БИС, а также реализации конвейерного типа выполнения команд в самой БИС. Микропроцессорная БИС может работать с памятью объемом до 1 Мбайта, обмениваться информацией с 64 Кбайтами внешних устройств, имеет 256 типов различных прерываний.

Обычно процесс выполнения команд программы в МП включает в себя следующие этапы: извлечение кода команды (операндов команды, если этого требует код команды) из памяти; выполнение команды; запись результата (если этого требует команда). Как правило, в МП все эти этапы выполняются последовательно, что приводит к недоиспользованию по временной загрузке магистралей микроЭВМ. В МП БИС К1810ВМ86 процесс выполнения команд состоит из тех же этапов, однако проводится в двух раздельных процессорных блоках (см. рис. 4.1, а): блоке выполнения команд (execution unit – EU) и блоке сопряжения с магистралями (Bus Interface Unit – BIU). В функции BIU входит извлечение из памяти кода команд и их операндов, а также запись результата в память. Блоки могут работать независимо друг от друга, и, следовательно, процессы преобразования и передачи информации в них могут идти параллельно.

Блок выполнения команд имеет 16-разрядное АЛУ с регистром состояния и флагами управления, а также регистры общего назначения. Все регистры и внутренние магистрали блока 16-разрядные. Блок не имеет связи с внешними магистралями МП БИС. На АЛУ поступают коды команд из конвейера команд, расположенного в BIU. Если в результате дешифрации кода команд в АЛУ необходимо получение одного или нескольких операндов по внешним магистралям МП БИС, то EU запрашивает BIU на получение и размещение необходимых данных в BIU. Несмотря на то, что все адреса, с которыми оперирует EU, 16-разрядные, BIU производит необходимое преобразование адресов так, чтобы EU имел возможность обращаться ко всему возможному адресному пространству (1 Мбайт) микропроцессорной системы.

Рис. 4.1. Упрощенная схема МП БИС КР1810 ВМ86

Блок сопряжения с магистралями производит все пересылки данных и кодов для EU. Пересылки между МП БИС и памятью или внешними устройства-ми осуществляются по требованию EU. В то время как EU занят выполнением команды, блок BIU получает последующие в программе коды команд из памяти и сохраняет их в конвейере команд. В конвейере может быть записано до шести кодов команд. Это позволяет BIU выдавать в EU сохраненные команды по мере необходимости без загрузки внешних магистралей МП БИС. Блок BIU организует получение нового кода команды, как только два байта в конвейере команд будут переданы в EU. За один цикл получения кода команды в блок BIU записываются с МД два байта команды.

В большинстве случаев в BIU находится хотя бы одна команда и EU не ждет, пока очередная команда будет извлечена из памяти.

Коды команд подаются в EU последовательно так, как они записаны в программе. Если EU выполняет команду передачи управления в другое место программы, то BIU очищает конвейер команд, получает код команды из нового адреса, передает его в EU и начинает заполнять конвейер заново. Если EU требует обращения к памяти или внешнему устройству, то BIU приостанавливает процесс получения команд в конвейер и организует необходимый цикл обмена данными.

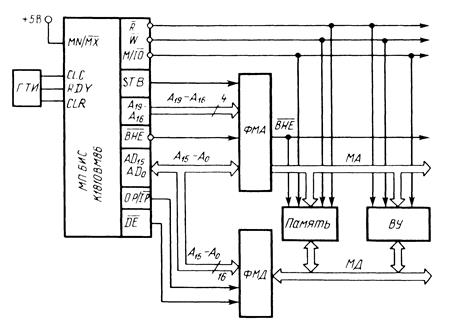

На рис. 4.2 приведен пример построения однопроцессорной системы.

Рис. 4.2. Структура микроЭВМ на базе МП БИС КР1810ВМ86

Основная задача, решаемая в многопроцессорных системах, заключается в обеспечении распределения времени доступа каждого из процессоров к общей системной магистрали. Магистрали микроЭВМ представляют собой систему MULTIBUS, в состав которой входят 16-разрядная МД, 20-разрядная МА, восемь входов прерываний, шины управления и шины арбитража. Последние позволяют осуществить синхронизацию процесса использования системных магистралей при параллельной работе нескольких процессоров в системе. Для формирования шин управления и арбитража в таких системах применяются специальная схема системного контроллера и схема арбитража работы процессоров. Схемы используют следующие выводы МП БИС: RQ/EQ, RQ/E1, позволяющие сопроцессорам брать управление магистралями системы; QS0 и QS1, отображающие состояние конвейера команд и позволяющие внешним устройством или сопроцессорам системы следить за выполнением команд МП БИС; LOCK – сигнал, используемый для запрета доступа к магистралям на время выполнения текущей команды.

Основная задача, решаемая в многопроцессорных системах, заключается в обеспечении распределения времени доступа каждого из процессоров к общей системной магистрали. Магистрали микроЭВМ представляют собой систему MULTIBUS, в состав которой входят 16-разрядная МД, 20-разрядная МА, восемь входов прерываний, шины управления и шины арбитража. Последние позволяют осуществить синхронизацию процесса использования системных магистралей при параллельной работе нескольких процессоров в системе. Для формирования шин управления и арбитража в таких системах применяются специальная схема системного контроллера и схема арбитража работы процессоров. Схемы используют следующие выводы МП БИС: RQ/EQ, RQ/E1, позволяющие сопроцессорам брать управление магистралями системы; QS0 и QS1, отображающие состояние конвейера команд и позволяющие внешним устройством или сопроцессорам системы следить за выполнением команд МП БИС; LOCK – сигнал, используемый для запрета доступа к магистралям на время выполнения текущей команды.

Дата: 2019-05-29, просмотров: 360.