Принцип моделирования 4-х разрядного счетчика на JK-триг-герах рассмотрим на примере схемы, приведенной на рисунке 1.

Заметим, что в модели каждого триггера имеется три входа J1, J2, J3 и три входа К1, К2, К3 объединяются через два элемента (находящихся в микросхеме), реализующих логическую операцию 3И. Поэтому на схеме (рис. 1) входы J1, J2, J3 и входы К1, К2, К3 объединены. Информация передается на входы J и входы К при перепаде тактового импульса с высокого уровня напряжения на низкий (при отрицательном фронте тактового импульса).

Перед поступлением счетных импульсов JK – триггеры U1, U2, U3, U4 должны быть установлены в состояние ‘0’. Для этого после вычерчивания схемы и задания профиля моделирования Transient с основным параметром Run to Time: 72 us следует открыть страницу с вкладкой Options, в разделе Category выбрать пункт Gate-level Simulation (Уровень узла моделирования), а затем в пункте Initialize all flip-flops to (Установить все переключения в) установить ‘0’.

При поступлении 1-го тактового импульса на вход CLK триггера U1, по его заднему фронту (по отрицательному фронту) триггер U1 переходит в состояние ‘1’. Задний фронт 2-го тактового импульса переводит U1 в состояние ‘0’, а отрицательный фронт на его выходе Q переводит триггер U2 в состояние ‘1’. Задний фронт 3-го тактового импульса переводит U1 в состояние ‘1’ и т. д.

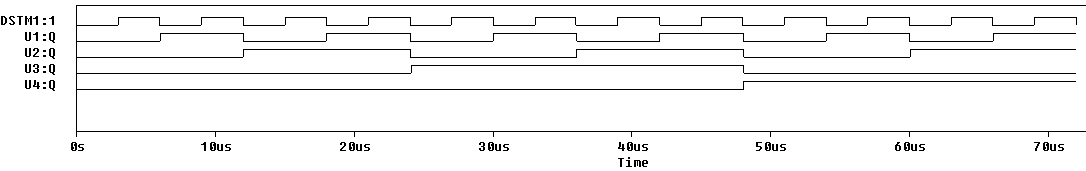

Временные диаграммы, характеризующие работу счетчика, приведенные на рисунке 2, получены для профиля моделирования Transient с параметрами Run to Time: 72us, Maximum step size:

0,07 us.

Задание 1. Создайте папку с именем Lab_rab4, имеющую путь доступа C:\Ivanov\Lab_rab4, а в ней создайте папки Zadanie1, Zadanie2 и запустите редактор Capture.

Начертите схему, представленную на рисунке 1, зная что:

– JK – триггер хранится в библиотеке 7400;

– размещение портов связи HI приведено в лабораторной работе № 3.

Отредактируйте свойства источников сигналов V1 и DSTM1, которые приведены на рисунке 1.

Создайте профиль моделирования Transient со следующими параметрами: Run to time: 72 us, Start saving data after: 0, Maximum step size: 0,07 us и сохраните его.

Запустите процесс моделирования, по окончанию которого отобразите временные диаграммы сигналов DSTM:1, U1:Q, U2:Q, U3:Q, U4:Q.

Занесите в отчет схему модели, приведенной на рисунке1, и полученные временные диаграммы.

Рис. 1. Модель 4-х разрядного счетчика на JK – триггерах

Рис. 2. Временные диаграммы, характеризующие работу схемы,

приведенной на рисунке 1

Модель синхронного реверсивного программируемого

Х разрядного счетчика

Модель синхронного реверсивного программируемого 4-х разрядного счетчика имеет имя 74191 и хранится в библиотеке 7400. Условное графическое изображение счетчика и схема его подключения к источнику тактовых сигналов и источникам напряжения приведена на рисунке 3.

Для работы компонента в режиме суммирующего счетчика необходимо:

– на вход  (Загрузка данных) подать напряжение высокого уровня;

(Загрузка данных) подать напряжение высокого уровня;

– на вход CTEN (Разрешение счета) подать напряжение низкого уровня;

– на вход D  / (Down/

/ (Down/  (Вычитание/суммирование)) подать напряжение низкого уровня;

(Вычитание/суммирование)) подать напряжение низкого уровня;

Эти напряжения подаются на указанные выходы компонента от источников постоянного напряжения V1, V2 через порты: HI – высокий уровень, LO – низкий уровень.

Импульсы, число которых подсчитывается, подаются от генератора тактовых сигналов DSTM1, имеющего свойства, указанные на рисунке 3.

Перед началом моделирования (после вычерчивания схемы и задания профиля моделирования) необходимо на странице с вкладкой Options выбрать раздел Category, в нем выбрать пункт Gate-level Simulation, а затем в пункте Initialize all flip-flops to установить ‘0’.

Таблица 1 – Режимы работы компонента 74191

| Вход | Выполняемая функция | |||

| CTEN | D/

| CLK | |

| 1 | 0 | 0 | Суммирование | |

| 1 | 0 | 1 | Вычитание | |

| 0 | X | X | X | Загрузка |

| 1 | 1 | X | X | Нет изменений |

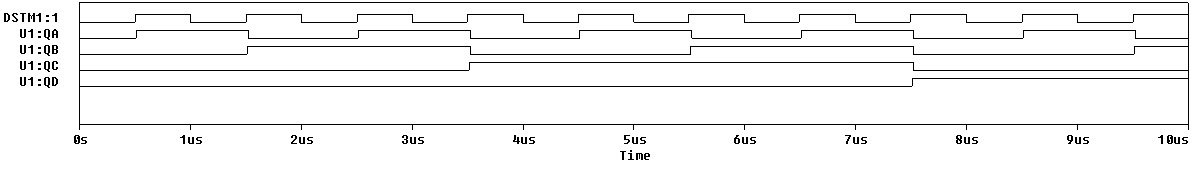

Результаты моделирования, полученные для профиля моделирования Transient с параметрами Run to time: 10 us, Start saving data after: 0, Maximum step size: 0.01us, приведены на рисунке 4.

Рис. 3. Модель схемы подключения счетчика к источнику тактовых сигналов и источникам напряжения

Рис. 4. Временные диаграммы, характеризующие работу схемы,

приведенной на рисунке 3

Задание 2. Запустите редактор Capture и начертите схему, представленную на рис. 3. Отредактируйте свойства источников сигналов V1, V2 и DSTM1.

Создайте профиль моделирования Transient со следующими параметрами: Run to time: 10 us, Start saving data after: 0, Maximum step size: 0,01us и сохраните его.

Запустите процесс моделирования, по окончанию которого отобразите временные диаграммы сигналов DSTM:1, U1:QA, U1:QB, U1:QC, U1:QD.

Занесите в отчет схему модели, приведенной на рис. 3, и полученные временные диаграммы.

Выполнение работы

1. Включите ПК и запустите редактор OrCad Capture.

2. Последовательно выполните задания 1 и 2, сохраняя проекты соответственно в папках Zadanie1 и Zadanie2.

Форма отчетности

Отчет должен содержать:

1. Цель работы и основные положения по пунктам 1.1, 1.2, 1.3.

2. Моделируемые схемы и временные диаграммы каждого задания.

4. Контрольные вопросы

1. Какие виды счетчиков применяются в цифровых схемах?

2. Поясните: последовательность моделирования схемы, приведенной на рис. 1; временные диаграммы, характеризующие её работу.

3. Поясните: последовательность моделирования схемы, приведенной на рис. 3; временные диаграммы, характеризующие её работу.

4. Поясните таблицу истинности компонента 74191.

Литература

1. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE: Пер. с нем. М.: ДМК Пресс, 2008. 336 с.: ил.

2. Новиков Ю. В. Введение в цифровую схемотехнику. Издательство: Интернет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. 344 с.: ил., табл. («Основы информационных технологий»).

ЛАБОРАТОРНАЯ РАБОТА № 5

Моделирование дешифраторов

Цель работы: приобрести навыки создания проектов моделирования дешифраторов; научиться получать временные диаграммы и проводить их анализ.

Основные положения

Дата: 2019-05-28, просмотров: 422.