СОДЕРЖАНИЕ

| Лабораторная работа № 1 Моделирование статических процессов смешанных аналоговых и цифровых электрических схем…………………………… | 4 |

| Лабораторная работа № 2 Моделирование аналого-цифровых схем……………………... | 14 |

| Лабораторная работа № 3 Моделирование динамических процессов в цифровых схемах с портами, генераторами тактовых и одноразрядных сигналов | 22 |

| Лабораторная работа № 4 Моделирование схем счетчиков импульсов…………………... | 29 |

| Лабораторная работа № 5 Моделирование дешифраторов………………………………... | 35 |

| Лабораторная работа № 6 Моделирование шифраторов…………………………………... | 44 |

| Литература……………………………………………………………. | 52 |

ЛАБОРАТОРНАЯ РАБОТА № 1

Моделирование статических процессов смешанных аналоговых

и цифровых электронных схем

Цель работы: приобрести навыки создания, сохранения проекта в системе OrCAD и черчения схем для моделирования статических режимов работы смешанных аналоговых и цифровых схем; на-учиться анализировать полученные результаты.

Основные сведения

В схемах цифровой техники часто применяют микросхемы средней степени интеграции транзисторно-транзисторной логики (ТТЛ).

Микросхемы серии ТТЛ семейства 7400 включают широкий функциональный набор логических элементов, триггеров и цифровых узлов. Напряжение питания микросхем – +5 В. При положительном кодировании (когда за высокий уровень принята единица, а за низкий уровень – нуль), уровень напряжения логического

0 составляет ≤ 0,4 В (L ≤ 0,4 V), а уровень напряжения логической

1 – ≥ 2,4 В (H ≥ 2,4 V). Модели микросхем семейства 7400 хранятся в библиотеке с именем 7400. Отечественными аналогами этого семейства являются семейства К133, К135, К555 и др.

Микросхемы серии КМОП семейства 4000 имеют быстродействие меньше, чем микросхемы семейства 7400, но предъявляют незначительные требования к источнику питания (напряжение можно подавать от +3 В до +18 В при очень малом токе). При положительном кодировании уровень напряжения логического

0 составляет ≤ 0,1 В (L≤0,1 V), а уровень напряжения логической

1 – ≥ 2,4 В (H ≥ 2,4 V). Модели микросхем семейства 4000 хранятся в библиотеке с именем 4000. Отечественными аналогами этого семейства являются семейства 176, 561, КР1554 и др.

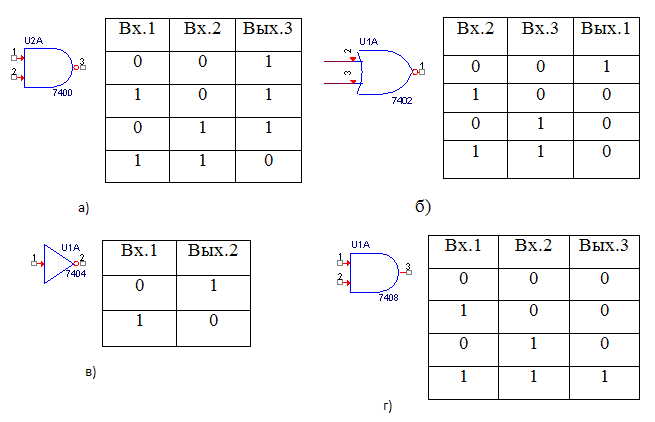

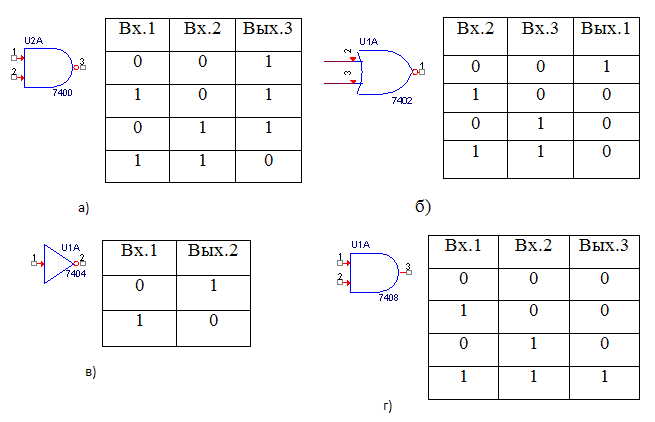

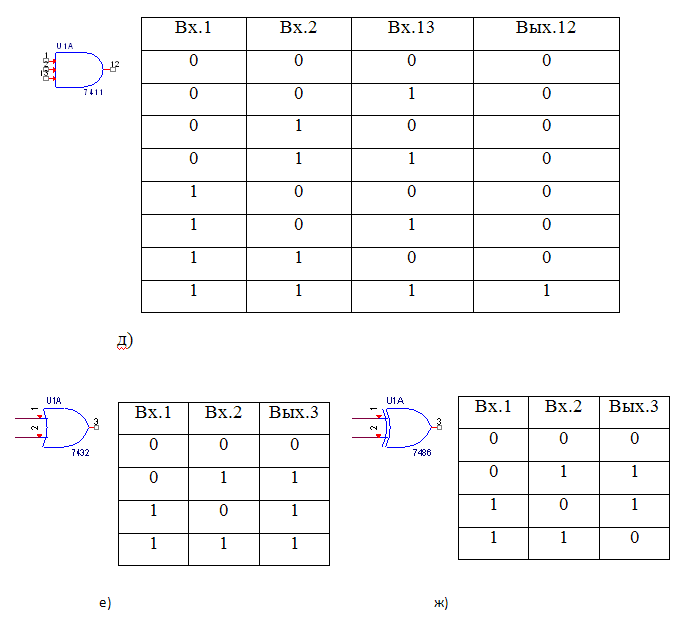

Графическое изображение некоторых логических компонентов и их таблицы истинности приведены на рисунке 1(а–ж).

Компонент 7400 содержит 4 логических элемента, каждый реализует логическую операцию «И-НЕ» с двумя входами и имеет таблицу истинности (рис. 1а).

Компонент 7402 содержит 4 логических элемента, каждый реализует логическую операцию «ИЛИ-НЕ» с двумя входами и имеет таблицу истинности (рис. 1б).

Компонент 7404 содержит 6 инверторов и имеет таблицу истинности (рис. 1в).

Компонент 7408 содержит 4 логических элемента, каждый реализует логическую операцию «И» с двумя входами и имеет таблицу истинности (рис. 1г).

Компонент 7411 содержит 3 логических элемента, каждый реализует логическую операцию «И» с тремя входами и имеет таблицу истинности (рис. 1д).

Компонент 7432 содержит 4 логических элемента, каждый реализует логическую операцию «ИЛИ» с двумя входами и имеет таблицу истинности (рис. 1е).

Компонент 7486 содержит 4 логических элемента, каждый реализует логическую операцию «Исключающее ИЛИ» с двумя входами и имеет таблицу истинности (рис. 1ж).

Следует знать, что в результате моделирования состояния компонентов отображаются следующим образом:

– состояние ‘логический нуль’ отображается символом ‘0’;

– состояние ‘логическая единица’ отображается символом ‘1’;

– неопределенное состояние отображается символом ‘X’.

Рис. 1. Графическое изображение логических компонентов

и их таблицы истинности.

Начало. Окончание на стр. 6.

Рис. 1. Графическое изображение логических компонентов

и их таблицы истинности.

Окончание. Начало на стр. 5.

2. Запуск редактора и создание нового проекта

моделирования цифровых электронных схем

Для запуска Capture и создания нового проекта моделирования цифровых электронных схем следует придерживаться следующих пунктов:

1. При помощи программы Проводник создайте папки, где будут храниться файлы будущего проекта, путь доступа к которым может выглядеть так: C:\EMb-14-1\Ivanov\ Lab_rab1\Zadanie1.

2. Из главного меню Windows запустите редактор, щёлкая последовательно по кнопке и пунктам:

<Пуск>→<Все программы>→< Cadence >→<Release 16.3>→<OrCAD Capture >, или дважды щёлкните по ярлыку редактора Capture на рабочем столе. На экране откроется рабочее окно редактора Capture, которое будет озаглавлено ‘OrCAD Capture’.

3. Приступите к созданию нового проекта, выбрав в меню File команду New, а затем пункт Projec.

4. В появившемся окне ‘New Project’:

– в поле Name введите имя проекта (например, Zadanie1);

– выберите опцию ‘Analog or Mixed A/D’ (‘Аналоговые или смешанные аналого-цифровые’);

– в поле Location (Размещение) укажите путь к ранее созданным папкам;

– щёлкнув по кнопке OK, закройте окно ‘New Project’.

5. В открывшемся окне ‘Create PSpice Project’ (‘Создать проект PSpice’), не изменяя содержимое поля ‘Analog GND Symbol. opj’ (‘Символ аналоговой ‘земли’), щёлкните по кнопке OK. После этого редактором Capture автоматически создается в папке Design Resources папка с именем Zadanie1.dsn и в рабочей области окна ‘OrCAD Capture’ открывается второе окно Организатора проекта с именем ‘C:\ Ivanov\ Lab_rab1’ и общим названием Analog or Mixed A/D. Это окно имеет две страницы с вкладками File (Файл) и

Hierarchy (Иерархия). На странице с вкладкой File отображается иерархическая структура проекта, которая предоставляет вам все возможности для его создания:

– щёлкнув по значку + разверните папку Zadanie1.dsn;

– щёлкнув по значку + разверните папку SCHEMATIC1;

– дважды щелкнув по папке PAGE1, откройте третье окно с вкладкой PAGE1 и заголовком ‘SCHEMATIC1:PAGE1’, которое накладывается на второе и является окном для ввода чертежа схемы.

Выделив символ ‘земля’, узел и линию (провод), а также текст на английском языке, удалите их, нажав клавишу Delete (Удалить).

Черчение схем проектов

При вычерчивании схемы проекта можно условно выделить следующие этапы:

– поиск и размещение нужных компонентов в окне

‘SCHEMATIC1:PAGE1’;

– соединение выводов компонентов с помощью проводников и/или шин.

При поиске и размещении компонентов в окне ‘SCHEMATIC1: PAGE1’ необходимо знать названия и содержимое библиотек компонентов. Так, например, часто применяемые в цифровых схемах компоненты хранятся в библиотеках с именем 7400 и 4000.

При щёлчке по кнопке  – Place part панели инструментов откройте окно ‘Place Part’ и выделите библиотеку с именем 7400.

– Place part панели инструментов откройте окно ‘Place Part’ и выделите библиотеку с именем 7400.

В поле Part окна ‘Place Part’ введите номер микросхемы 7404. Редактором Capture автоматически будет найден символ инвертора 7404 и отображен в левой нижней части окна ‘Place Part’. Поместите его на своем чертеже, для этого щёлкните по кнопке  окна‘Place Part’ или Enter на клавиатуре, после чего символ инвертора ‘прилипнет’ к указателю ‘мыши’. Переместив указатель ‘мыши’ в нужное место расположения первого инвертора, щелчком левой кнопки ‘мыши’ разместите первый его экземпляр. Переместив указатель ‘мыши’ с символом инвертора правее, щелчком разместите его второй экземпляр и т. д. Не перемещая указатель ‘мыши’, щёлкните правой кнопкой ‘мыши’ и в открывшемся меню щёлкните по опции End Mode, завершите размещение инверторов.

окна‘Place Part’ или Enter на клавиатуре, после чего символ инвертора ‘прилипнет’ к указателю ‘мыши’. Переместив указатель ‘мыши’ в нужное место расположения первого инвертора, щелчком левой кнопки ‘мыши’ разместите первый его экземпляр. Переместив указатель ‘мыши’ с символом инвертора правее, щелчком разместите его второй экземпляр и т. д. Не перемещая указатель ‘мыши’, щёлкните правой кнопкой ‘мыши’ и в открывшемся меню щёлкните по опции End Mode, завершите размещение инверторов.

Сохранение проекта

Чтобы сохранить созданный проект необходимо последовательно щёлкнуть по: <File>→<Save>, или щёлкнуть по кнопке ‘Save document’ (Сохранить документ).

Задание 1. Начертите схему, представленную на рисунке 2, точно выбирая имена компонентов из библиотеки 7400, задав напряжения источникам V1, V2, V3 – 5V. При этом профиль моделирования Bias создаётся системой автоматически.

Запустите процесс моделирования, по окончанию которого включите кнопку  и занесите в отчет схему с указанием логических состояний каждого компонента. Сохраните проект.

и занесите в отчет схему с указанием логических состояний каждого компонента. Сохраните проект.

Задание 2. В схеме, представленной на рисунке 3, подключите на выход компонента U6 A резистор с сопротивлением 180 Om, как показано на рисунке 9.

Запустите процесс моделирования, по окончанию которого включите кнопку  и занесите в отчет схему, с указанием логических состояний каждого компонента.

и занесите в отчет схему, с указанием логических состояний каждого компонента.

Обратите внимание на то, что на выходе компонента 7486 появится напряжение 1,967 V, которое переводит компонент 7432 в неопределенное состояние, обозначаемое буквой Х.

Рис. 2. Схема с различными компонентами цифровой техники

Задание 3. В схеме, представленной на рисунке 3, включите формирователь напряжения на транзисторе BC548 B (который находится в библиотеке EBIPOLER) на выход компонента U6 A, как показано на рисунке 4. Этот формирователь задаёт напряжение, переключающее компонент U7 A в состояние логической единицы.

Запустите процесс моделирования, по окончанию которого включите кнопку  и занесите в отчет схему, с указанием логических состояний каждого компонента и напряжений каскада на транзисторе Q1.

и занесите в отчет схему, с указанием логических состояний каждого компонента и напряжений каскада на транзисторе Q1.

Рис. 3. Цифровая схема, в которой напряжение 1,967 V

на входе 2 компонента U7 A приводит его в неопределённое состояние

Рис. 4. Цифровая схема с формирователем напряжения на транзисторе

Выполнение работы

3.1. Включите ПК и запустить редактор OrCad Capture.

3.2. Выполните задания 1, 2, 3.

Форма отчетности

Отчет должен содержать:

– цель работы и основные положения по пунктам 1 и 2;

– схемы, представленные на рисунках 2–4 с результатами моделирования, определенными в заданиях.

5. Контрольные вопросы

1. Какие микросхемы применяются в цифровой технике, их основные характеристики?

2. Приведите таблицу истинности для логических компонентов 7400, 7408,7486.

3. Приведите таблицу истинности для логических компонентов 7402, 7404,7411, 7432.

4. Поясните результаты моделирования задания 1.

5. Поясните результаты моделирования задания 2.

6. Поясните результаты моделирования задания 3.

Литература

1. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE: Пер. с нем. М.: ДМК Пресс, 2008. 336 с.: ил.

2. Новиков Ю. В. Введение в цифровую схемотехнику. Издательство: Интернет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. 344 с.: ил., табл. («Основы информационных технологий»).

ЛАБОРАТОРНАЯ РАБОТА № 2

Моделирование аналого-цифровых схем

Цель работы: приобрести навыки создания проекта моделирования аналого-цифровых схем; освоить работу с модулем Probe; научиться получать временные диаграммы дискретных процессов и проводить их анализ.

Основные сведения

Основной целью моделирования аналого-цифровых электронных схем является исследование протекающих в них переходных процессов. Для этого в модуле PSpice используется анализ типа Transient (Переходный процесс) и при практической работе создается профиль с именем ‘SCHEMATIC1-transient’. После выполнения необходимых расчетов, модулем PSpice присваиваются узлам и выводам компонентов моделируемой схемы строго определенные обозначения, которые отображаются в левой части окна модуля Probe и называются списком диаграмм. Список диаграмм содержит три вида обозначений:

– аналоговые напряжения (относительно ‘земли’) обозначаются как и в аналоговых схемах. К ним добавляются только обозначения ‘земли’ (например, V(U1A:GND)) и цифрового напряжения питания (например, V (U1A:VCC)). Здесь: V – символ отображаемого напряжения, U1A – имя компонента схемы, GND – имя ‘земли’, а VCC – имя источника питания для компонента U1A;

– для узлов и соединений, на которых расположены как аналоговые, так и цифровые компоненты, наряду с указанием аналоговых напряжений есть также указание цифровых состояний. Например: U1A:Y – дискретный выход инвертора U1A; V(U1B:Y) – аналоговый выход инвертора U1B;

– для узлов и соединений, на которых находятся исключительно цифровые компоненты, указываются только цифровые состояния, например U1A:Y.

Чтобы легче разбираться в списке диаграмм, часто узлам и соединениям присваиваются псевдонимы. Например, входному узлу присваивается псевдоним in, выходному узлу – псевдоним out и

т. д. Естественно, что каждая аналого-цифровая схема имеет свои особенности не только в обозначениях самих компонентов, но и их входов и выходов. Поэтому особенности моделирования аналого-цифровых схем следует рассматривать на конкретных примерах.

Рис. 1. Аналого-цифровая схема с двумя инверторами

Задание 1. Создайте проект анализа работы простейшей аналого-цифровой схемы, приведенной на рисунке 1. Получите, проанализируйте и занесите в отчет временные диаграммы входного, выходного напряжений и цифрового состояния на выходе 2 инвертора U1A. Увеличьте фрагмент диаграмм на отрезке времени от 495 us до 505 us и при помощи курсора определите, и занесите в отчет длительность интервала неопределенного состояния U1A и уровни его выходного напряжения при переключении.

Создайте папку с именем Lab_rab2, имеющую путь доступа C:\EMb-14-1\Ivanov\Lab_rab2, а в ней папку Zadanie1 и запустите редактор CAPTURE.

Начертите схему, приведенную, на рисунке 1.

Для этого откройте окно ‘Place Part’, в поле Part которого введите имя символа источника импульсного напряжения: VPULSE, расположенного в библиотеке Source, и расположите его на рабочей поверхности. Разместите две модели инвертора 7404 (библиотека 7400) и символ резистора R1 (библиотека Analog), трижды повернув его против часовой стрелки нажатием клавиши R. Сделайте необходимые соединения.

1.1. Редактирование свойств компонентов

Отредактируйте свойства источника импульсного напряжения. Для этого двойным щелчком по символу компонента VPULSE откройте окно ‘Property Editor’, в котором отредактируйте значения обязательных свойств:

– V1=0V – нижний уровень напряжения (при начале импульса);

– V2=5V – верхний уровень напряжения (высота импульса);

– TD=0,5ms – время задержки начала импульса;

– TR=1us – длительность переднего фронта импульса (время нарастания импульса);

– TF=1us – длительность заднего фронта импульса (время затухания импульса);

– PW=0,498ms – длительность плоской вершины импульса (ширина импульса);

– PER=1ms – период следования (повторения) импульсов.

Остальные свойства оставьте без изменений.

Присвойте соединению на входе U1A псевдоним in, соединению на выходе U1B – псевдоним out, а соединению между двумя инверторами – midl. Для этого щёлкните по < Place (Разместить)>→ <Net Alias…(Рамка псевдонима…)>. В открывшемся окне ‘Place Net Alias’ введите в поле Alias: in и щёлкните по кнопке ‘OK’, закройте это окно. После этого к указателю ‘мыши’ ‘прилипает’ прямоугольник (рамка), нижнюю сторону которого совместите с соединением источника напряжения V1 и инвертора U1A. Щелчком левой кнопки ‘мыши’ закрепите псевдоним соединения, затем щёлкните по правой кнопке и в открывшемся меню щёлкните по опции End Mode (Конец режима работы). Аналогично установите псевдоним для соединения выхода первого инвертора U1A с входом второго инвертора U1В – midl и псевдоним соединения выхода второго инвертора U1B с резистором R1 – out.

Выполнение работы

1. Включить ПК и запустить редактор OrCad Capture.

2. Выполните задания 1 и 2.

Форма отчетности

Отчет должен содержать:

1. Цель работы и основные положения по пункту 1.

2. При выполнении задания 1 приведите:

– аналого-цифровую схему (рис. 1);

– основные свойства компонента VPULSE;

– диаграммы V(in), V(out), V(midl) и измеренные V(in), V(out).

3. При выполнении задания 2 приведите:

– увеличенный фрагмент диаграммы, измеренные уровни напряжений неопределенного состояния инвертора и длительности его интервала времени.

4. Контрольные вопросы

1. Представьте временную диаграмму (на интервале времени от 0s до 2ms) импульсного напряжения источника, имеющего следующие свойства:

V1=5 V, V2=–5 V, TD=0 s, TR=0,1 us, TF=0,1 us, PW=498 us, PER=1 ms.

2. Поясните временную диаграмму, приведенную на рисунке 3. Каковы уровни выходного напряжения инвертора U1A, определяющие его неопределенное состояние?

3. Поясните временную диаграмму, полученную при исследовании области перехода на интервале времени от 490 us до 510 us. Чем определяется увеличение интервала времени неопределенного состояния инвертора U1 A?

4. Почему в задании 2 увеличился уровень напряжения на выходе инвертора U1 B?

Литература

1. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE: Пер. с нем. М.: ДМК Пресс, 2008. 336 с.: ил.

2. Новиков Ю. В. Введение в цифровую схемотехнику. Издательство: Интернет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. 344 с.: ил., табл. («Основы информационных технологий»).

ЛАБОРАТОРНАЯ РАБОТА № 3

И одноразрядных сигналов

Цель работы: освоить технику работы с генератором тактовых сигналов DSTM, одноразрядным источником входных сигналов STIM1 и портами связи. Научиться получать временные зависимости цифровых процессов в логических элементах и проводить необходимые измерения.

Основные сведения

Выполнение работы

3.1. Включите ПК и запустите редактор OrCad Capture.

3.2. Выполните задания 1, 2.

Форма отчетности

Отчет должен содержать:

– цель работы и основные положения по пункту 1;

– схемы, представленные на рисунке 2 и рисунке 4 с результатами моделирования, определенными в заданиях.

4. Контрольные вопросы

1. Перечислите источники напряжения и их свойства в цифровых схемах.

2. Назовите логические состояния и приведите их изображения в Probe.

3. Что применяется в качестве элемента связи в цифровых схемах?

4. Поясните временные диаграммы, приведенные на рисунке 3.

5. Поясните временные диаграммы, приведенные на рисунке 5.

Литература

1. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE: Пер. с нем. М.: ДМК Пресс, 2008. 336с.: ил.

2. Новиков Ю. В. Введение в цифровую схемотехнику. Издательство: Интернет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. 344 с.: ил., табл. («Основы информационных технологий»).

ЛАБОРАТОРНАЯ РАБОТА № 4

Основные положения

Общие сведения о счетчиках

Счетчиком называется функциональный узел устройства обработки информации, предназначенный для подсчета числа импульсов, поступающих на его вход.

Счет числа поступающих импульсов производится в двоичной системе счисления. Обычно простые счетчики разделяются на: суммирующие, вычитающие и реверсивные.

Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т. е. для сложения. С поступлением очередного импульса на вход счетчика его показание увеличивается на единицу.

Вычитающий счетчик служит для осуществления счета в обратном направлении, т. е. для вычитания. Каждый импульс, поступающий на вход вычитающего счетчика, уменьшает его показание на единицу.

Реверсивный счетчик предназначен для операции счета, как в прямом, так и в обратном направлении, т. е. он может работать в режиме сложения и вычитания.

Основными показателями счетчиков являются коэффициент счета и быстродействие.

Коэффициент счета Ксч определяет число импульсов, которое может быть сосчитано счетчиком. Ксч определяется числом разрядов двоичного числа n: Ксч =2n.

Быстродействие счетчика характеризуется максимальной частотой следования счетных импульсов и связанным с ней временем установки счетчика. Время установки определяется максимальным временем протекания переходных процессов во всех разрядах счетчика при поступлении на вход очередного счетного импульса.

Для хранения одного разряда двоичного числа применяется один триггер. Поэтому счетчик можно рассматривать как «связанную цепочку» n триггеров. Связи определяются типом применяемых триггеров.

Х разрядного счетчика

Модель синхронного реверсивного программируемого 4-х разрядного счетчика имеет имя 74191 и хранится в библиотеке 7400. Условное графическое изображение счетчика и схема его подключения к источнику тактовых сигналов и источникам напряжения приведена на рисунке 3.

Для работы компонента в режиме суммирующего счетчика необходимо:

– на вход  (Загрузка данных) подать напряжение высокого уровня;

(Загрузка данных) подать напряжение высокого уровня;

– на вход CTEN (Разрешение счета) подать напряжение низкого уровня;

– на вход D  / (Down/

/ (Down/  (Вычитание/суммирование)) подать напряжение низкого уровня;

(Вычитание/суммирование)) подать напряжение низкого уровня;

Эти напряжения подаются на указанные выходы компонента от источников постоянного напряжения V1, V2 через порты: HI – высокий уровень, LO – низкий уровень.

Импульсы, число которых подсчитывается, подаются от генератора тактовых сигналов DSTM1, имеющего свойства, указанные на рисунке 3.

Перед началом моделирования (после вычерчивания схемы и задания профиля моделирования) необходимо на странице с вкладкой Options выбрать раздел Category, в нем выбрать пункт Gate-level Simulation, а затем в пункте Initialize all flip-flops to установить ‘0’.

Таблица 1 – Режимы работы компонента 74191

| Вход | Выполняемая функция | |||

| CTEN | D/

| CLK | |

| 1 | 0 | 0 | Суммирование | |

| 1 | 0 | 1 | Вычитание | |

| 0 | X | X | X | Загрузка |

| 1 | 1 | X | X | Нет изменений |

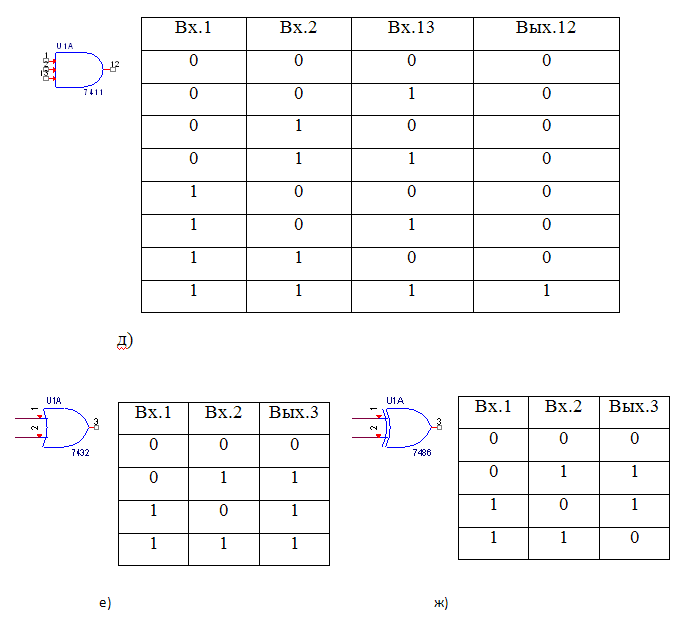

Результаты моделирования, полученные для профиля моделирования Transient с параметрами Run to time: 10 us, Start saving data after: 0, Maximum step size: 0.01us, приведены на рисунке 4.

Рис. 3. Модель схемы подключения счетчика к источнику тактовых сигналов и источникам напряжения

Рис. 4. Временные диаграммы, характеризующие работу схемы,

приведенной на рисунке 3

Задание 2. Запустите редактор Capture и начертите схему, представленную на рис. 3. Отредактируйте свойства источников сигналов V1, V2 и DSTM1.

Создайте профиль моделирования Transient со следующими параметрами: Run to time: 10 us, Start saving data after: 0, Maximum step size: 0,01us и сохраните его.

Запустите процесс моделирования, по окончанию которого отобразите временные диаграммы сигналов DSTM:1, U1:QA, U1:QB, U1:QC, U1:QD.

Занесите в отчет схему модели, приведенной на рис. 3, и полученные временные диаграммы.

Выполнение работы

1. Включите ПК и запустите редактор OrCad Capture.

2. Последовательно выполните задания 1 и 2, сохраняя проекты соответственно в папках Zadanie1 и Zadanie2.

Форма отчетности

Отчет должен содержать:

1. Цель работы и основные положения по пунктам 1.1, 1.2, 1.3.

2. Моделируемые схемы и временные диаграммы каждого задания.

4. Контрольные вопросы

1. Какие виды счетчиков применяются в цифровых схемах?

2. Поясните: последовательность моделирования схемы, приведенной на рис. 1; временные диаграммы, характеризующие её работу.

3. Поясните: последовательность моделирования схемы, приведенной на рис. 3; временные диаграммы, характеризующие её работу.

4. Поясните таблицу истинности компонента 74191.

Литература

1. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE: Пер. с нем. М.: ДМК Пресс, 2008. 336 с.: ил.

2. Новиков Ю. В. Введение в цифровую схемотехнику. Издательство: Интернет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. 344 с.: ил., табл. («Основы информационных технологий»).

ЛАБОРАТОРНАЯ РАБОТА № 5

Моделирование дешифраторов

Цель работы: приобрести навыки создания проектов моделирования дешифраторов; научиться получать временные диаграммы и проводить их анализ.

Основные положения

И входом сброса (74259)

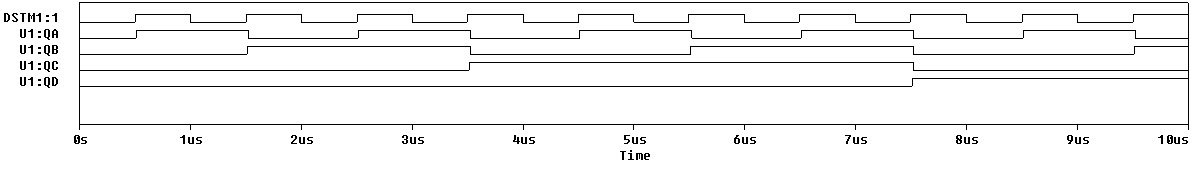

Графическое изображение модели дешифратор 74259 представ-лено на рисунке 4. Модель хранится в библиотеке компонентов системы OrCAD 16,3, имеющей имя 7400.

Модель имеет группу входов S0, S1, S2, на котрые подаётся двоичный код (от 000 до 111), и группу выходов Q0, Q1,…Q7, с которых считываются сигналы. С помощью сигналов, подаваемых на вход размещения работы  и выход

и выход  (очистка), можно задавать следующие режимы работы модели.

(очистка), можно задавать следующие режимы работы модели.

1. Очистка буферного регистра: реализуется при подаче на вход  сигнала высокого уровня, а на выход

сигнала высокого уровня, а на выход  – сигнала низкого уровня.

– сигнала низкого уровня.

При этом на всех выходах (Q0÷Q7) формируется напряжение низкого уровня.

Рис. 4. Модель дешифратора 74259

2. Режим дешифрации с выборкой одного сигнала из восьми реализуется при подаче на входы  и

и  сигналов низкого уровня. При этом на вход D следует задать сигнал высокого уровня (5 В).

сигналов низкого уровня. При этом на вход D следует задать сигнал высокого уровня (5 В).

3. Режим передачи информации с входа D на один из 8-ми выходов. Этот режим реализуется при подаче на вход  сигнала низкого уровня, а на вход

сигнала низкого уровня, а на вход  сигнала высокого уровня. При этом уровни сигналов на входах S0, S1, S2 определяют адрес передачи, т. е. на какой из 8-ми выходов будет передаваться информация с входа D. На всех остальных выходах сохраняется напряжение высокого уровня.

сигнала высокого уровня. При этом уровни сигналов на входах S0, S1, S2 определяют адрес передачи, т. е. на какой из 8-ми выходов будет передаваться информация с входа D. На всех остальных выходах сохраняется напряжение высокого уровня.

Например, если на вход S0 подается напряжение высокого уровня, а на входы S1, S2 – низкого, то на выходе Q1 устанавливается такое же напряжение, как и входе D, а на выходах Q0 и Q2–Q7 формируется напряжение низкого уровня.

4. Режим хранения данных. Реализуется при подаче на вход  и

и  сигналов высокого уровня. При этом в буферный регистр записывается текущая информация. Входы S0–S2 в этом режиме не влияют на работу модели.

сигналов высокого уровня. При этом в буферный регистр записывается текущая информация. Входы S0–S2 в этом режиме не влияют на работу модели.

Таблица 1 – Режимы работы дешифратора74259

| Вход | Режим работы | |

|

| |

| 1 | 0 | Очистка |

| 0 | 0 | Дешифрация |

| 0 | 1 | Передача информации |

| 1 | 1 | Хранение данных |

Таблица 2 – Сигналы входов и выходов

| Адресный вход | Адресуемый выход | ||

| S2 | S1 | S0 | |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 2 |

| 0 | 1 | 1 | 3 |

| 1 | 0 | 0 | 4 |

| 1 | 0 | 1 | 5 |

| 1 | 1 | 0 | 6 |

| 1 | 1 | 1 | 7 |

Время задержки передачи сигнала (в зависимости от типа микросхемы) 7,5÷14 нсек, потребляемый ток – 22÷60мА.

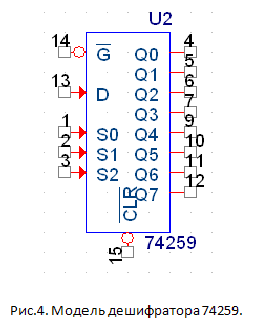

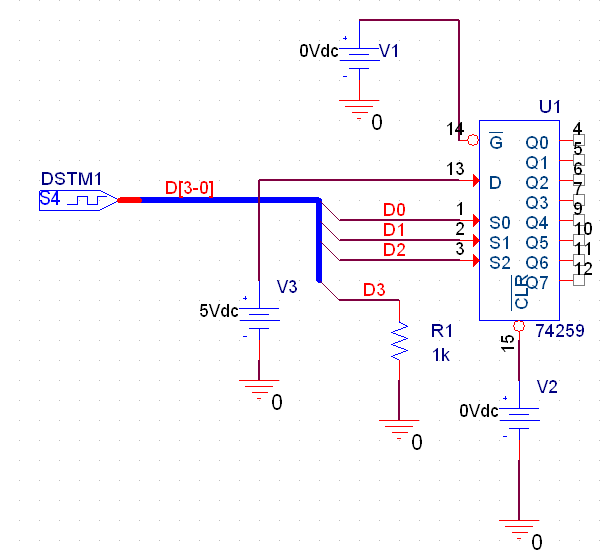

Рассмотрим модель схемы подключения источников сигналов и напряжений, которая иллюстрирует режим дешифрации 3-х разрядного двоичного кода.

При черчении схемы неиспользуемая четвертая линия передачи шины источника сигналов DSTM1 через резистор – эквивалент с сопротивлением 1 кОм, должна быть соединена с землей.

Свойства программируемого источника входных сигналов для 4-х разрядной шины задаются следующими командами:

COMMAND1 – 0ms 0000; COMMAND2 – 1 ms 0001; COMMAND3 – 2ms 0010;

COMMAND4 – 3ms 0011; COMMAND5 – 4 ms 0100; COMMAND6 – 5ms 0101.

Анализ работы модели во временной области задаётся профилем ‘Time Domain (Transient)’, имеющим следующие параметры: Run to Time: 5.5ms.

Рис. 5. Модель схемы подключения источников напряжения

и сигналов к дешифратору 74259

Задание 1. Создайте папку с именем Lab_rab5, имеющую путь доступа C:\Ivanov\Lab_rab5, а в ней создайте папки Zadanie1 и Zadanie2, запустите редактор Capture.

Начертите схему, представленную на рисунке 2.

Отредактируйте свойства источника сигналов DSTM1, задав значения: COMMAND1 – 0 ms 0000; COMMAND2 – 1 ms 0001; COMMAND3 – 2 ms 0010; COMMAND4 – 3 ms 0011;COMMAND5 – 4 ms 0100; COMMAND6 – 5 ms 0101;

COMMAND7 – 6 ms 0110; COMMAND8 – 7 ms 0111; COMMAND9 – 8 ms 1000; COMMAND10 – 9 ms 1001.

Создайте профиль моделирования Transient со следующими параметрами: Run to time: 10 ms и сохраните его. Затем откройте страницу с вкладкой Options. В разделе Category выбрать пункт Gate-level Simulation (Уровень узла моделирования), а затем в пункте Initialize all flip-flops to (Установить все переключения в) установить ‘0’.

Рис. 6. Временные диаграммы работы дешифратора 74259

Напомним, что при черчении модели схемы шине и четырём её линиям передачи данных обязательно присваиваются имена (псевдонимы), как описано в лабораторной работе № 2.

Запустите процесс моделирования, по окончанию которого создайте 6 систем координат. Для этого щёлкните 6 раз по: <Plot (Чертеж)>→<Add Plot to Window (Добавить чертеж окно). Щёлкнув по <Trace>→<Add Trace>, откройте окно ‘Add Traces’и отобразите временные диаграммы сигналов в следующей последовательности:

– в верхней D0, D1, D2, D3;

– в следующих: V(U1:Y0), V(U1:Y1), V(U1:Y2), V(U1:Y3), V(U1:Y4) .

Занесите в отчет схему модели, приведенной на рисунке 2, и полученные временные диаграммы.

Задание 2. Начертите схему, представленную на рисунке 5. Отредактируйте свойства источника сигналов DSTM1 задав значения:

COMMAND1 – 0 ms 0000; COMMAND2 – 1 ms 0001; COMMAND3 – 2 ms 0010COMMAND4 – 3 ms 0011; COMMAND5 – 4 ms 0100; COMMAND6 – 5 ms 0101.

Создайте профиль моделирования Transient со следующими параметрами: Run to time: 5,5 ms и сохраните его.

Запустите процесс моделирования, по окончанию которого создайте 2 системы координат, отобразите временные диаграммы сигналов D0, D1, D2, U1:Q0, U1:Q1, U1:Q2, U1:Q3, U1:Q4, U1:Q5, U1:Q6, U1:Q7, как показано на рис.6. Занесите в отчет полученные временные диаграммы и поясните их.

Выполнение работы

1. Включите ПК и запустите редактор OrCad Capture.

2. Последовательно выполните задания 1 и 2, сохраняя проекты соответственно в папках Zadanie1 и Zadanie2.

Форма отчетности

Отчет должен содержать:

1. Цель работы и основные положения по пунктам 1.1, 1.2 и 1.3.

2. Моделируемые схемы и временные диаграммы каждого задания.

4. Контрольные вопросы

1. Поясните назначение дешифраторов.

2. Перечислите входы и выходы модели дешифратора 7445 и поясните их назначение.

3. Перечислите входы и выходы модели дешифратора 74259 и поясните их назначение.

4. Поясните временные диаграммы, полученные при выполнении задания 1.

5. Поясните временные диаграммы, полученные при выполнении задания 2.

Литература

1. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE: Пер. с нем. М.: ДМК Пресс, 2008. 336с.: ил.

2. Новиков Ю. В. Введение в цифровую схемотехнику. Издательство: Интернет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. 344 с.: ил., табл. («Основы информационных технологий»).

ЛАБОРАТОРНАЯ РАБОТА № 6

Моделирование шифраторов

Цель работы: приобрести навыки создания проектов моделирования шифраторов; научиться получать временные диаграммы и проводить их анализ.

Основные положения

Общие сведения о шифраторах

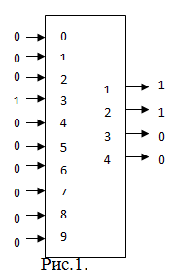

Шифратором называется комбинационная схема, которая пре-образует один из десяти входных сигналов в 4-х разрядный двоичный выходной сигнал. Это преобразование условно можно представить следующим образом: при появлении сигнала высокого

| уровня (‘1’) на одном из входов (рис. 1 вход 3) – на выходах появляются сигналы, представляю-щие 4-х разрядный двоичный код (0011) номера входа. Одно из основных применений шифратора – это ввод данных с клавиатуры десяточных чисел. Нажатие клавиши с одной из десятичных цифр приводит к формированию и передаче в другие узлы двоичного кода этой цифры. Существует несколько видов шифраторов. Например, шифраторы, которые при одновременном нажа-тии нескольких клавиш вырабаты- |

Рис. 1. Схема работы шифратора

вают код только старшей цифры, называются приоритетными. Для увеличения разрядности выходно-го кода применяют несколько шифраторов, выходы которых объ-диняются с помощью элементов, реализующих простые логические операции. Эта процедура называется каскадированием шифраторов.

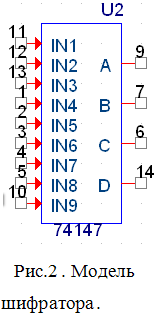

1.2. Модель шифратора для преобразования десятичных чисел в двоичный код с приоритетом (74147)

| Графическое изображение модели шифратора представлено на рисунке 2. Модель хранится в библиотеке с именем 7400 и позволяет расположить 9 входных сигналов в последовательности согласно приоритету сигнала. Приоритет (важность) сигнала определяется десятичным номером входа. Модель также служит как шифратор клавиатуры или как обычный шифратор десятичного числа в 4-х разрядный двоичный код. |

Рис. 2. Модель шифратора 74147

Модель имеет 9 входов (IN1 – IN9), на каждый из которых подаётся сигнал, имеющий низкий уровень напряжения ‘0’ или высокий –‘1’. На 4-х выходах (D, C, B, A) модели формируется инверсный 4-х разрядный двоичный код, соответствующий десятичному номеру входа, имеющему низкий уровень. Говорят, что для данной модели активным является низкий уровень входного сигнала.

Если на входы не подаются сигналы низкого уровня, то на всех выходах устанавливается сигнал высокого уровня, что в инверсном коде соответствует десятичному числу 0.

Если сигнал низкого уровня подаётся на один из входов, то на выходе формируется инверсный двоичный код, соответствующий десятичному номеру данного входа. Например, если напряжение низкого уровня подается на вход IN6, то на выходах устанавливаются следующие значения D=1, C=0, B=0,A=1, т. е. двоичное число 1001. Цифра 6 в двоичной системе имеет вид 0110, а при активном низком уровне сигнала, т. е. в инверсном виде, она равна 1001.

Если на два и более входа одновременно подаются сигналы низкого уровня, то на выходах (D, C, B, A) формируется инверсный код, соответствующий входу с наибольшим порядковым номером (наивысшим приоритетом), а состояние остальных входов игнорируется. Например, когда на входы IN4 и IN6 одновременно подаются сигналы низкого уровня, выходной инверсный сигнал устанавливается равным 1001. Если же на входы IN4 и IN7 одновременно подаются сигналы низкого уровня, то выходной инверсный сигнал будет равен 1000 (что в прямом коде равно 0111 и цифре в двоичной системе счисления 7). Модель работает без использования тактовых импульсов и не имеет буферного регистра. В каждый момент времени низкий уровень сигнала на входе, имеющем наивысший приоритет, появляется на выходах в виде своего инверсного двоичного эквивалента. Работа модели шифратора 74147 представлена в таблице 1.

Таблица 1 – Работа модели шифратора 74147

| Входы | Выходы | |||||||||||

| IN1 | IN2 | IN3 | IN4 | IN5 | IN6 | IN7 | IN8 | IN9 | D | C | B | A |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| X | X | X | X | X | X | X | X | 0 | 0 | 1 | 1 | 0 |

| X | X | X | X | X | X | X | 0 | 1 | 0 | 1 | 1 | 1 |

| X | X | X | X | X | X | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| X | X | X | X | X | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| X | X | X | X | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| X | X | X | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| X | X | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| X | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

Технические данные стандартной микросхемы 74147:

– время задержки прохождения сигнала 10 нс.;

– ток потребления 45 мА.

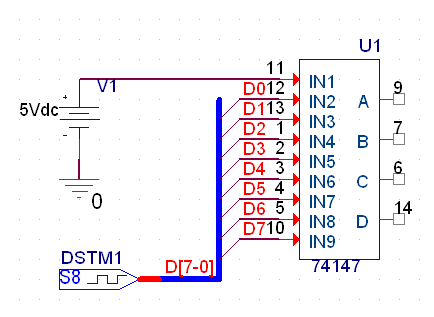

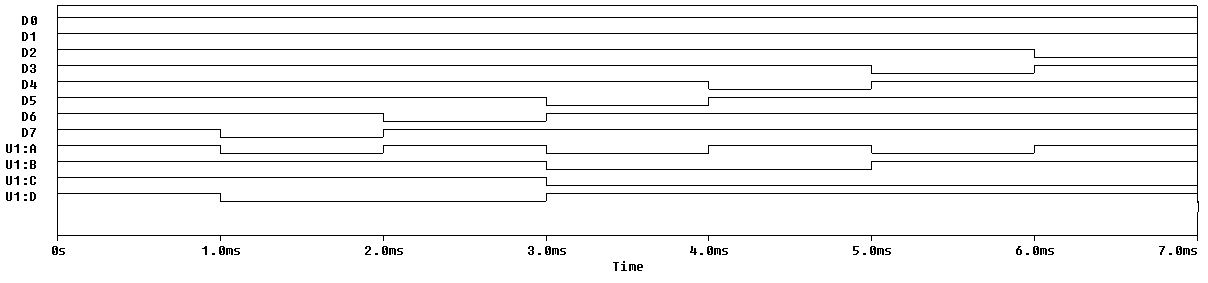

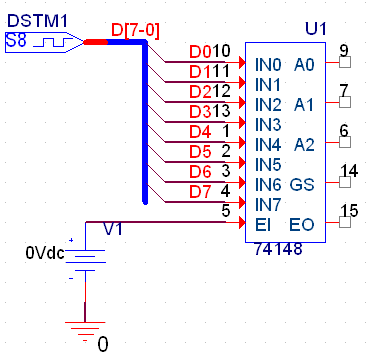

Рис. 3. Модель схемы подключения источников сигналов

к модели шифратора 74147

В схеме применены программируемый 8-ми разрядный источник входных сигналов DSTM1 и источник напряжения высокого уровня V1.

Для получения временых диаграмм, соответствующих уровням сигналов, указанным в шести строках таблицы 1, следует выбрать профиль моделирования Transient с основными параметрами Run to time: 6 ms и задать следующие свойства источнику DSTM1: COMMAND1 0 ms 11111111; COMMAND2 1 ms 01111111; COMMAND3

2 ms 10111111; COMMAND4 3 ms 11011111; COMMAND5 4 ms 11101111; COMMAND6 5 ms 11110111; COMMAND7 6 ms 11111011.

Рис. 4. Временные диаграммы,

иллюстрирующие работу шифратора 74147

1.3. Модель шифратора для преобразования восьми десятичных чисел (от 0 до 7) в 3-х разрядный двоичный код

С приоритетом (74148)

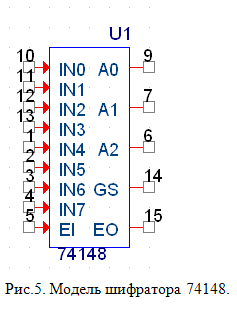

Рис. 5. Модель шифратора 74148

Графическое изображение модели шифратора представлено на рисунке 5. Модель хранится в библиотеке с именем 7400 и позволяет расположить 8 входных сигналов в последовательности согласно приоритету важности сигнала. Чем больше число, подаваемое на вход, тем выше его приоритет. Модель может использоваться как обычный шифратор десятичного числа в 3-х разрядный двоичный код.

Модель имеет 8 входов (IN0, IN1,..,IN7), на каждый из которых подается сигнал, имеющий низкий уровень ‘0’ или высокий ‘1’. На трех выходах (А2, А1, А0) формируется инверсный 3-х разрядный двоичный код, соответствующий десятичному номеру входа, имеющему низкий уровень сигнала.

Для данной модели активным является низкий уровень входного сигнала. Если на все входы подается сигнал высокого уровня, а на вход IN0 – низкого, то на всех выходах (А2, А1, А0) устанавливается сигнал высокого уровня, т. е. инверсный код 111, которому соответствует прямой код 000.

Если сигнал низкого уровня подается только на вход IN3, то на выходах устанавливаются следующие значения: А2=1, А1=0, А0=0. Этому инверсному двоичному коду соответствует прямой код 011.

Если на два или более входа одновременно подаются сигналы низкого уровня, то на выходах (А2, А1, А0) формируется инверсный код, соответствующий входу с наибольшим порядковым номером (наивысшим приоритетом), а состояние остальных входов игнорируется. Например, когда на входы IN1 и IN4 одновременно подаются сигналы низкого уровня, выходной инверсный сигнал установится равным 011 (что в прямом коде равно 100 и цифре в десятичной системе счисления 4).

Кроме 7 информационных входов (IN0, IN1,…,In7) и 3-х выходов (А2, А1, А0) в модели имеются еще 2 выхода GS и EO. Эти выходы используются для каскадного соединения моделей. На выходе GS формируется сигнал низкого уровня, если такой сигнал подаётся на какой-либо из входов. На выходе ЕО формируется сигнал высокого уровня, когда такой сигнал подаётся на разрешающий вход EI. В нормальном режиме работы на вход EI должен подаваться сигнал низкого уровня. Работа модели шифратора 74148 представлена в таблице 2.

Таблица 2 – Работа модели шифратора 74148

| Входы | Выходы | ||||||||||||

| EI | IN0 | IN1 | IN2 | IN3 | IN4 | IN5 | IN6 | IN7 | A2 | A1 | A0 | GS | E0 |

| 0 | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | X | X | X | X | X | X | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | X | X | X | X | X | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | X | X | X | X | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | X | X | X | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | X | X | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | X | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

Технические данные стандартной микросхемы 74148:

– время задержки прохождения сигнала 10 нсек;

– ток потребления 38 мА.

Рассмотрим модель схемы подключения источников сигналов, которая иллюстрирует режим шифрации модели 74148.

Рис. 6. Модель схемы подключения источника сигналов

к модели шифратора 74148

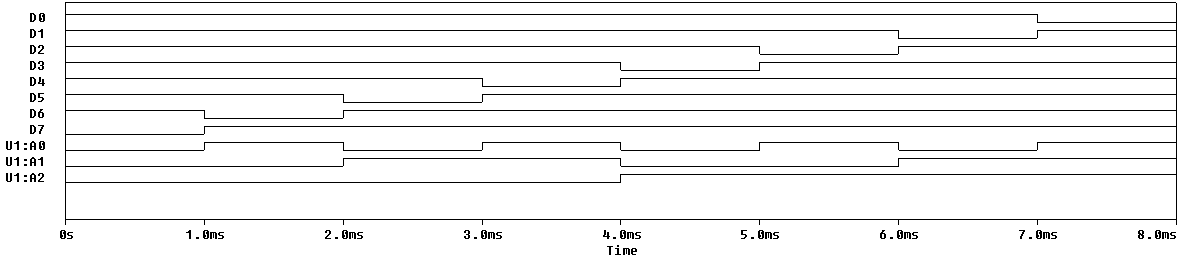

Для получения временых диаграмм, соответствующих уровням сигналов, указанным в семи строках таблицы 2, следует выбрать профиль моделирования Transient с основными параметрами Run to time: 8ms и задать следующие свойства источнику DSTM1: COMMAND1 – 0 ms 01111111; COMMAND2 – 1 ms 10111111; COMMAND3 – 2 ms 11011111; COMMAND4 – 3 ms 11101111; COMMAND5 – 4 ms 11110111; COMMAND6 – 5 ms 11111011; COMMAND7 – 6 ms 11111101; COMMAND8 – 7 ms 11111110.

Рис. 7. Временные диаграммы, иллюстрирующие работу шифратора 74148

Задание 1. Создайте папку с именем Lab_rab6, имеющую путь доступа C:\EMb-11-1\Ivanov\Lab_rab6, а в ней создайте папку Zadanie1 и Zadanie2, запустите редактор Capture.

Начертите схему, представленную на рисунке 3. Отредактируйте свойства:

– источника питания V1;

– свойства источника сигналов DSTM1, как было приведено выше.

Напомним, что при черчении модели схемы шине и восьми её линиям передачи данных обязательно присваиваются имена (псевдонимы).

Создайте профиль моделирования Transient со следующими параметрами: Run to time: 7us и сохраните его. Затем откройте страницу с вкладкой Options. В разделе Category выбрать пункт Gate-level Simulation (Уровень узла моделирования), а затем в пункте Initialize all flip-flops to (Установить все переключения в) установить ‘0’.

Запустите процесс моделирования, по окончанию которого отобразите временные диаграммы входных сигналов: D0, D1, D2, D3, D4, D5, D6, D7; и выходных U1:A, U1:B, U1:C, U1:D. Занесите в отчет полученные временные диаграммы и поясните их.

Задание 2. Начертите схему, представленную на рисунке 6. Отредактируйте свойства:

– источника питания V1;

– свойства источника сигналов DSTM1, как было приведено выше.

Напомним, что при черчении модели схемы шине и восьми её линиям передачи данных обязательно присваиваются имена (псевдонимы).

Создайте профиль моделирования Transient со следующими параметрами: Run to time: 8ms и сохраните его. Затем откройте страницу с вкладкой Options. В разделе Category выбрать пункт Gate-level Simulation (Уровень узла моделирования), а затем в пункте Initialize all flip-flops to (Установить все переключения в) установить ‘0’.

Запустите процесс моделирования, по окончанию которого отобразите временные диаграммы входных сигналов: D0, D1, D2, D3, D4, D5, D6, D7; и выходных U1:A0, U1:A1, U1:A2. Занесите в отчет полученные временные диаграммы и поясните их.

Выполнение работы

1. Включите ПК и с помощью программы Проводник создайте папку для хранения проекта.

2. Запустите редактор OrCad Capture.

3. Последовательно выполните задания 1 и задание 2, сохраняя проекты в папках Zadanie1 и Zadanie2.

Форма отчетности

Отчет должен содержать:

1. Цель работы и основные положения по пунктам 1.1, 1.2 и 1.3.

2. Моделируемые схемы и временные диаграммы каждого задания.

4. Контрольные вопросы

1. Поясните назначение шифраторов.

2. Перечислите входы и выходы модели шифратора 74147 и поясните их назначение.

3. Перечислите входы и выходы модели дешифратора 74148 и поясните их назначение.

4. Поясните временные диаграммы, полученные при выполнении задания 1.

5. Поясните временные диаграммы, полученные при выполнении задания 2.

Литература

1. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE: пер. с нем. М.: ДМК Пресс, 2008. 336с.: ил.

2. Новиков Ю. В. Введение в цифровую схемотехнику. Издательство: Интернет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. 344 с.: ил., табл. («Основы информационных технологий»).

МОДЕЛИРОВАНИЕ УЗЛОВ

ЦИФРОВЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

ВЛАДИКАВКАЗ 2015

СОДЕРЖАНИЕ

| Лабораторная работа № 1 Моделирование статических процессов смешанных аналоговых и цифровых электрических схем…………………………… | 4 |

| Лабораторная работа № 2 Моделирование аналого-цифровых схем……………………... | 14 |

| Лабораторная работа № 3 Моделирование динамических процессов в цифровых схемах с портами, генераторами тактовых и одноразрядных сигналов | 22 |

| Лабораторная работа № 4 Моделирование схем счетчиков импульсов…………………... | 29 |

| Лабораторная работа № 5 Моделирование дешифраторов………………………………... | 35 |

| Лабораторная работа № 6 Моделирование шифраторов…………………………………... | 44 |

| Литература……………………………………………………………. | 52 |

ЛАБОРАТОРНАЯ РАБОТА № 1

Моделирование статических процессов смешанных аналоговых

и цифровых электронных схем

Цель работы: приобрести навыки создания, сохранения проекта в системе OrCAD и черчения схем для моделирования статических режимов работы смешанных аналоговых и цифровых схем; на-учиться анализировать полученные результаты.

Основные сведения

В схемах цифровой техники часто применяют микросхемы средней степени интеграции транзисторно-транзисторной логики (ТТЛ).

Микросхемы серии ТТЛ семейства 7400 включают широкий функциональный набор логических элементов, триггеров и цифровых узлов. Напряжение питания микросхем – +5 В. При положительном кодировании (когда за высокий уровень принята единица, а за низкий уровень – нуль), уровень напряжения логического

0 составляет ≤ 0,4 В (L ≤ 0,4 V), а уровень напряжения логической

1 – ≥ 2,4 В (H ≥ 2,4 V). Модели микросхем семейства 7400 хранятся в библиотеке с именем 7400. Отечественными аналогами этого семейства являются семейства К133, К135, К555 и др.

Микросхемы серии КМОП семейства 4000 имеют быстродействие меньше, чем микросхемы семейства 7400, но предъявляют незначительные требования к источнику питания (напряжение можно подавать от +3 В до +18 В при очень малом токе). При положительном кодировании уровень напряжения логического

0 составляет ≤ 0,1 В (L≤0,1 V), а уровень напряжения логической

1 – ≥ 2,4 В (H ≥ 2,4 V). Модели микросхем семейства 4000 хранятся в библиотеке с именем 4000. Отечественными аналогами этого семейства являются семейства 176, 561, КР1554 и др.

Графическое изображение некоторых логических компонентов и их таблицы истинности приведены на рисунке 1(а–ж).

Компонент 7400 содержит 4 логических элемента, каждый реализует логическую операцию «И-НЕ» с двумя входами и имеет таблицу истинности (рис. 1а).

Компонент 7402 содержит 4 логических элемента, каждый реализует логическую операцию «ИЛИ-НЕ» с двумя входами и имеет таблицу истинности (рис. 1б).

Компонент 7404 содержит 6 инверторов и имеет таблицу истинности (рис. 1в).

Компонент 7408 содержит 4 логических элемента, каждый реализует логическую операцию «И» с двумя входами и имеет таблицу истинности (рис. 1г).

Компонент 7411 содержит 3 логических элемента, каждый реализует логическую операцию «И» с тремя входами и имеет таблицу истинности (рис. 1д).

Компонент 7432 содержит 4 логических элемента, каждый реализует логическую операцию «ИЛИ» с двумя входами и имеет таблицу истинности (рис. 1е).

Компонент 7486 содержит 4 логических элемента, каждый реализует логическую операцию «Исключающее ИЛИ» с двумя входами и имеет таблицу истинности (рис. 1ж).

Следует знать, что в результате моделирования состояния компонентов отображаются следующим образом:

– состояние ‘логический нуль’ отображается символом ‘0’;

– состояние ‘логическая единица’ отображается символом ‘1’;

– неопределенное состояние отображается символом ‘X’.

Рис. 1. Графическое изображение логических компонентов

и их таблицы истинности.

Начало. Окончание на стр. 6.

Рис. 1. Графическое изображение логических компонентов

и их таблицы истинности.

Окончание. Начало на стр. 5.

2. Запуск редактора и создание нового проекта

моделирования цифровых электронных схем

Для запуска Capture и создания нового проекта моделирования цифровых электронных схем следует придерживаться следующих пунктов:

1. При помощи программы Проводник создайте папки, где будут храниться файлы будущего проекта, путь доступа к которым может выглядеть так: C:\EMb-14-1\Ivanov\ Lab_rab1\Zadanie1.

2. Из главного меню Windows запустите редактор, щёлкая последовательно по кнопке и пунктам:

<Пуск>→<Все программы>→< Cadence >→<Release 16.3>→<OrCAD Capture >, или дважды щёлкните по ярлыку редактора Capture на рабочем столе. На экране откроется рабочее окно редактора Capture, которое будет озаглавлено ‘OrCAD Capture’.

3. Приступите к созданию нового проекта, выбрав в меню File команду New, а затем пункт Projec.

4. В появившемся окне ‘New Project’:

– в поле Name введите имя проекта (например, Zadanie1);

– выберите опцию ‘Analog or Mixed A/D’ (‘Аналоговые или смешанные аналого-цифровые’);

– в поле Location (Размещение) укажите путь к ранее созданным папкам;

– щёлкнув по кнопке OK, закройте окно ‘New Project’.

5. В открывшемся окне ‘Create PSpice Project’ (‘Создать проект PSpice’), не изменяя содержимое поля ‘Analog GND Symbol. opj’ (‘Символ аналоговой ‘земли’), щёлкните по кнопке OK. После этого редактором Capture автоматически создается в папке Design Resources папка с именем Zadanie1.dsn и в рабочей области окна ‘OrCAD Capture’ открывается второе окно Организатора проекта с именем ‘C:\ Ivanov\ Lab_rab1’ и общим названием Analog or Mixed A/D. Это окно имеет две страницы с вкладками File (Файл) и

Hierarchy (Иерархия). На странице с вкладкой File отображается иерархическая структура проекта, которая предоставляет вам все возможности для его создания:

– щёлкнув по значку + разверните папку Zadanie1.dsn;

– щёлкнув по значку + разверните папку SCHEMATIC1;

– дважды щелкнув по папке PAGE1, откройте третье окно с вкладкой PAGE1 и заголовком ‘SCHEMATIC1:PAGE1’, которое накладывается на второе и является окном для ввода чертежа схемы.

Выделив символ ‘земля’, узел и линию (провод), а также текст на английском языке, удалите их, нажав клавишу Delete (Удалить).

Черчение схем проектов

При вычерчивании схемы проекта можно условно выделить следующие этапы:

– поиск и размещение нужных компонентов в окне

‘SCHEMATIC1:PAGE1’;

– соединение выводов компонентов с помощью проводников и/или шин.

При поиске и размещении компонентов в окне ‘SCHEMATIC1: PAGE1’ необходимо знать названия и содержимое библиотек компонентов. Так, например, часто применяемые в цифровых схемах компоненты хранятся в библиотеках с именем 7400 и 4000.

При щёлчке по кнопке  – Place part панели инструментов откройте окно ‘Place Part’ и выделите библиотеку с именем 7400.

– Place part панели инструментов откройте окно ‘Place Part’ и выделите библиотеку с именем 7400.

В поле Part окна ‘Place Part’ введите номер микросхемы 7404. Редактором Capture автоматически будет найден символ инвертора 7404 и отображен в левой нижней части окна ‘Place Part’. Поместите его на своем чертеже, для этого щёлкните по кнопке  окна‘Place Part’ или Enter на клавиатуре, после чего символ инвертора ‘прилипнет’ к указателю ‘мыши’. Переместив указатель ‘мыши’ в нужное место расположения первого инвертора, щелчком левой кнопки ‘мыши’ разместите первый его экземпляр. Переместив указатель ‘мыши’ с символом инвертора правее, щелчком разместите его второй экземпляр и т. д. Не перемещая указатель ‘мыши’, щёлкните правой кнопкой ‘мыши’ и в открывшемся меню щёлкните по опции End Mode, завершите размещение инверторов.

окна‘Place Part’ или Enter на клавиатуре, после чего символ инвертора ‘прилипнет’ к указателю ‘мыши’. Переместив указатель ‘мыши’ в нужное место расположения первого инвертора, щелчком левой кнопки ‘мыши’ разместите первый его экземпляр. Переместив указатель ‘мыши’ с символом инвертора правее, щелчком разместите его второй экземпляр и т. д. Не перемещая указатель ‘мыши’, щёлкните правой кнопкой ‘мыши’ и в открывшемся меню щёлкните по опции End Mode, завершите размещение инверторов.

Редактирование свойств компонентов схемы

Для того чтобы начерченная схема точно соответствовала заданной, компонентам следует задать нужные имена и определить их характеристики. При работе с редактором Capture имена, значения и другие характеристики компонентов называются свойствами ( Properties ). Свойства задаются в окне ‘Property

Editor’ (‘Редактор свойств’) или в окне ‘Display Properties’ (‘Отобразить свойства’). Окно ‘Property Editor’ открывается двойным щелчком по символу компонента, а окно ‘Display Properties’ – двойным щелчком по значению компонента.

Дата: 2019-05-28, просмотров: 441.