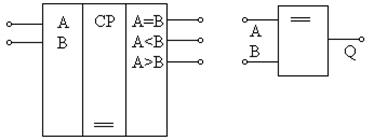

Компаратор – КИС, предназначенная для сравнения двух двоичных чисел.

УГО:

| А | В | A=B | A<B | A>B |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

Таблица состояний:

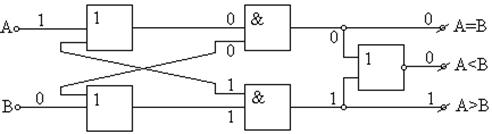

ФАЛ:

Внутренняя структурная схема включает в себя 2 элемента «НЕ», 2 – «И», 1 – «ИЛИ НЕ».

Условное обозначение: R564ИП2

Область применения:

- для выбора заданного числа в цифровой последовательности;

- для задания нужного времени в часах;

- для организации условных переходов в программирующих схемах МП-систем.

Последовательностные цифровые устройства.

Последовательностные ИС – устройства, в которых выходной сигнал определяется не только комбинацией входных сигналов, но и внутренним состоянием схемы, которое зависит от всей последовательности поступивших до этого входных сигналов.

К ним относят:

- триггеры;

- счетчики импульсов;

- регистры.

Триггеры.

Триггер – ИС, имеющая два состояния устойчивого равновесия, способная скачком переходить из одного устойчивого состояния в другое под действием внешнего управляющего сигнала.

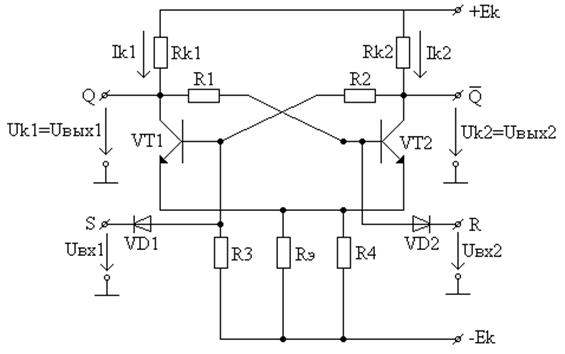

Схемное решение триггеров.

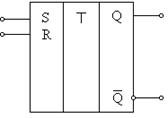

УГО:

Принцип действия:

В основе лежит уравнение Кирхгофа: Uвых=Ек-IкRк. В силу невзаимозаменяемости биполярных транзисторов всегда оказывается, что один из транзисторов открыт чуть больше другого.

Если VT1 открыт больше VT2, то Iк1> Iк2, т.е.  .

.

Процесс идет скачком, пока VT1 полностью открыт, а VT2 полностью закрыт. Это первое условие равновесия триггера. Его внутренняя схема представляет собой 2ух-каскадный УПТ с перекрестными 100%-ными положительными обратными связями R1 и R2. Описанное состояние триггер способен сохранять сколь угодно долгое время, пока на его входы не поступит управляющий сигнал (отрицательный внешний импульс). При поступлении отрицательного импульса на вход SET-установка VT1 скачком закроется, а VT2 откроется, в результате,  . Если подать отрицательный сигнал на вход закрытого транзистора, то его состояние не изменится (на вход RESET-сброс).

. Если подать отрицательный сигнал на вход закрытого транзистора, то его состояние не изменится (на вход RESET-сброс).

Постулат триггера состоит в следующем: на одном выходе триггера должна быть единица, на другом – 0, и наоборот.

Если объединить входы SET и RESET, и подавать входные импульсы сразу на оба входа, то триггер будет изменять свое выходное состояние при поступлении каждого входного импульса. Такой триггер назвали Т-триггером или счетным триггером.

Классификация триггеров.

1. По времени срабатывания:

1.1. Асинхронные триггеры, которые срабатывают в любой момент времени при появлении информации одновременно на обоих информационных входах S и R.

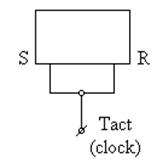

1.2. Синхронные триггеры, которые срабатывают при поступлении строб-сигналов.

1.2.1. Статические триггеры, которые срабатывают при определенном уровне строб-сигнала.

1.2.1.1. Однотактные триггеры.

1.2.1.2. 2ух-тактные триггеры.

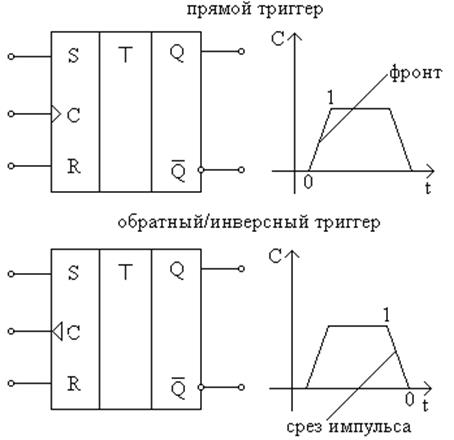

1.2.2. Динамические триггеры, которые срабатывают на фронте или на срезе строб-сигнала.

2. По функциональному назначению:

2.1. RS-триггеры;

2.2. D-триггеры;

2.3. счетные Т-триггеры;

2.4. JK-триггеры или универсальные триггеры.

Асинхронные RS-триггеры.

Асинхронные RS-триггеры выполняются или на элементах «ИЛИ-НЕ» или на элементах «И-НЕ», причем во внутренней логической схеме триггера должны присутствовать по 2 логических элемента, охваченных 100%-ми перекрестными обратными связями.

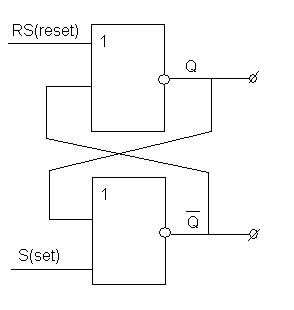

1. ИЛИ-НЕ.

Структурно-логическая схема:

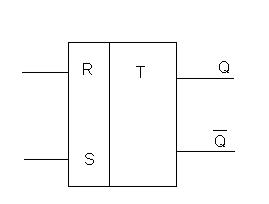

УГО:

Срабатывает при сигналах высокого уровня. Асинхронный RS-триггер имеет 2 информационных входа (set, reset), и 2 выхода (Q,  ).

).

Таблица истинности:

| R | S |

|

|

|

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | ||||

| 0 | 1 | 0 | 0 | 1 | 0 | Активизация (установка единицы) |

| 1 | 0 | 0 | 0 | 0 | 1 | Сброс (установка нуля) |

| 0 | 0 | 0 | 1 | 0 | 1 | Память (предыдущее состояние) |

| 1 | 1 | 0 | 0 | 0 | 0 | Неустойчивое состояние |

Триггер фактически двухтактный, т.к. в момент времени t – информация записывается в триггер, а в момент времени t+1 – переносится на выходы.

Наличие еа выходе триггера активных сигналов для схемы ИЛИ-НЕ, триггер находится в неустойчивом состоянии, поэтому такая комбинация входных сигналов называется запрещенной.

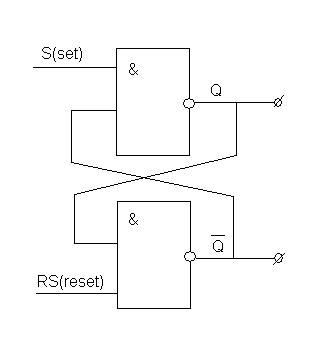

2. И-НЕ.

Структурно-логическая схема:

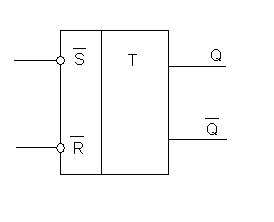

УГО:

Срабатывает при сигналах низкого уровня.

Таблица истинности:

|

|

|

|

|

| CОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | ||||

| 0 | 1 | 1 | 1 | 1 | 0 | Активизация |

| 1 | 0 | 1 | 1 | 0 | 1 | Сброс |

| 1 | 1 | 0 | 1 | 0 | 1 | Память |

| 0 | 0 | 1 | 1 | 1 | 1 | Неустойчивое состояние |

0,0 – недопустимая комбинация входных сигналов, для триггеров на элементах ИЛИ-НЕ.

Синхронные RS-триггеры.

1. ИЛИ-НЕ.

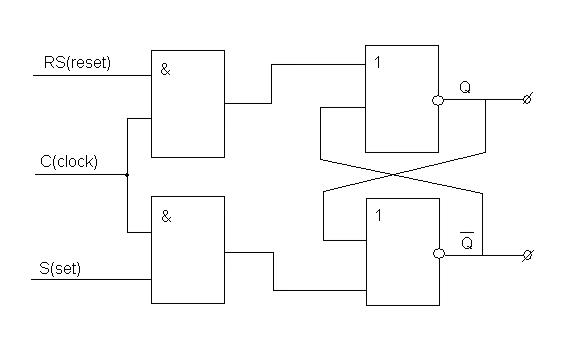

Структурно-логическая схема:

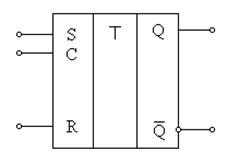

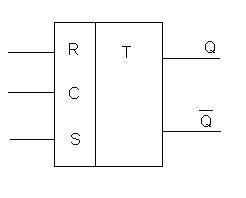

УГО:

Таблица состояний:

| C | R | S |

|

|

|

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | |||||

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | Память |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | Активизация |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | Сброс |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | Неустойчивое состояние |

2. И-НЕ.

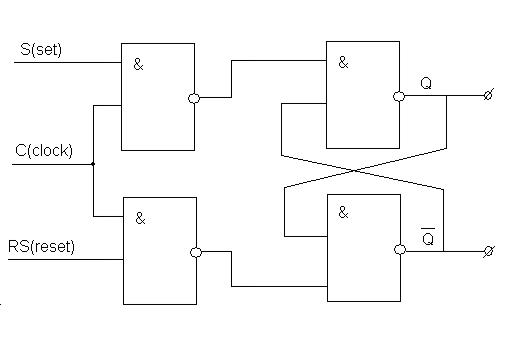

Структурно-логическая схема:

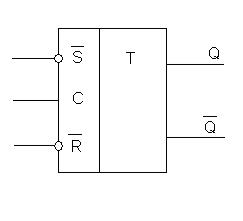

УГО:

Таблица состояний:

К недостаткам асинхронных и синхронных RS-триггеров относят:

1) наличие запрещенных комбинаций входных сигналов;

2) необходимость подачи сразу двух сигналов: на вход set и на вход reset.

Область применения: только в качестве элементов в ячейках памяти.

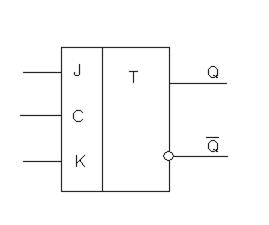

Счетные триггеры или Т-триггеры { T - такт}.

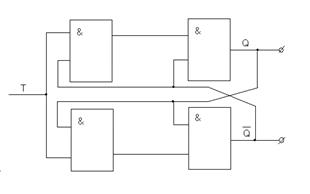

Структурно-логическая схема:

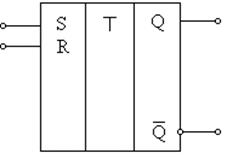

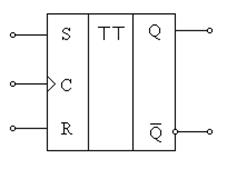

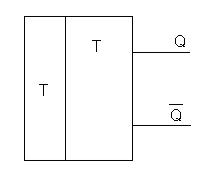

УГО:

Таблица состояний:

| T |

|

|

|

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | |||

| 0 | 0 | 1 | 0 | 1 | Память |

| 1 | 0 | 1 | 1 | 0 | Первый импульс |

| 1 | 0 | 1 | 0 | 1 | Второй импульс |

Счетный триггер меняет состояние своих выходов, при поступлении каждого нового сигнала на вход.

D-триггеры { D – delay – защелка, задержка}.

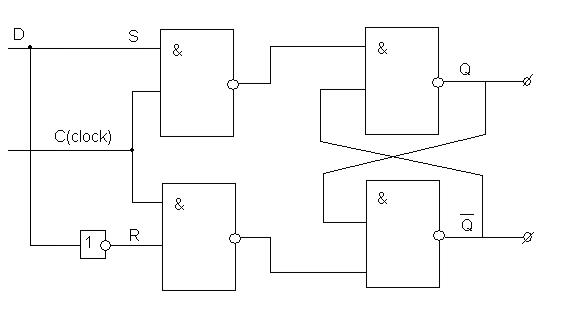

Структурно-логическая схема:

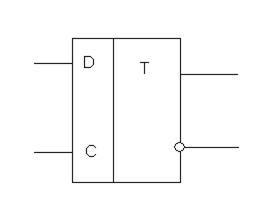

УГО:

В D-триггере имеется один информационный вход и 1 вход синхронизации (разрешения, стробирования). Одновременная подача на вход S и R противоположных по знаку сигнала, за счет внутреннего инвертирования сигнала D, с помощбю элемента НЕ.

Таблица истинности:

Универсальный JK-триггер{JK – jump keep}.

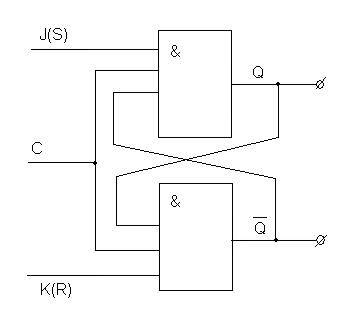

Структурно-логическая схема:

УГО:

Таблица состояний:

| С | J | R | Q |

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | |||

| 1 | 1 | 1 | 1 | 0 | Режим счета (1 импульс) |

| 1 | 1 | 1 | 0 | 1 | Режим счета |

Для организации режима счета, на входы J и K подаются одинаковые сигналы логической единицы.

Если на С единица, а на J – 1, K – 0, или J – 0, K – 1, то режим данных, причем, если на выходе:

Q – 1,  - 0 – активизация;

- 0 – активизация;

Q – 0,  -1 – сброс.

-1 – сброс.

Триггер называется универсальным, потому что, если все 3 входа соединить, то получаем режим счетчика; если на J подать сигнал от D, а на К, через инвертор, то получаем D-триггер.

Область применения: счетные триггеры применяются для счета команд в МП-системах, для счета адресов, для счета циклов выполняемых команд; D-триггеры применяют в различных регистрах, схемах памяти, при записи и считывании информации.

Счетчики импульсов.

Счетчик – последовательностное цифровое устройство, предназначенное для счета входных сигналов.

Классификация.

1. По направлению счета различных суммирований, которыми каждый входной сигнал вызывает инкремент выходного сигнала:

1.1. Вычитающий уменьшение выходного сигнала – декремент;

1.2. Реверсный, осуществляющий либо инкремент, либо декремент, в зависимости от содержания строб-сигнала.

2. По организации межразрядных связей:

2.1. с последовательным переносом информации между разрядами;

2.2. с параллельным переносом информации между разрядами.

3. В зависимости от коэффициента пересчета (модуль счетчика):

3.1. двоичные à  , где k – число разрядов;

, где k – число разрядов;

3.2. ДДК à  , где k – любое.

, где k – любое.

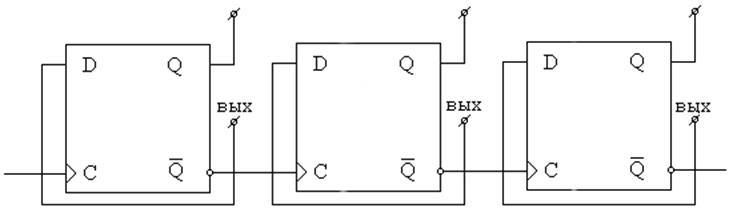

Физическое осуществление счетчиков.

Счетчики выполняются на триггерах, количество которых является разрядностью передаваемой информации. Триггеры соединены последовательно (прямо или инверсно) со счетным входным последующим переносом.

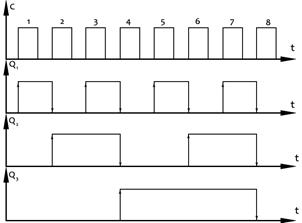

З-ех разрядный суммирующий счетчик с последовательным переносом.

В D-триггере информация со входа D подается на прямой выход. При последовательном переносе осуществляется последовательное срабатывание триггеров. В данном случае D-триггеры прямые динамические, срабатывание осуществляется на входе счетного импульса.

Таблица истинности.

| С | Т1 | Т2 | Т3 | Выходное двоичное слово | Десятичный эквивалент | |||

| Q1 |

| Q2 |

| Q3 |

| |||

| Исходное состояние | 0 | 1 | 0 | 1 | 0 | 1 | 000 | 0 |

| 1ый импульс 0à1 | 1 | 0 | 0 | 1 | 0 | 1 | 001 | 1 |

| 2ой импульс 0à1 | 0 | 1 | 1 | 0 | 0 | 1 | 010 | 2 |

| 3ий импульс 0à1 | 1 | 0 | 1 | 0 | 0 | 1 | 011 | 3 |

| 4ый импульс 0à1 | 0 | 1 | 0 | 1 | 1 | 0 | 100 | 4 |

| 5ый импульс 0à1 | 1 | 0 | 0 | 1 | 1 | 0 | 101 | 5 |

| 6ой импульс 0à1 | 0 | 1 | 1 | 0 | 1 | 0 | 110 | 6 |

| 7ой импульс 0à1 | 1 | 0 | 1 | 0 | 1 | 0 | 111 | 7 |

| 8ой импульс 0à1 | 0 | 1 | 0 | 1 | 0 | 1 | 000 | 0 |

Основные параметры счетчиков.

1. Модуль счета/коэффициент пересчета – количество импульсов, поступающих на вход, после которых внутренняя схема приходит в исходное состояние.

Модуль – отношение числа импульсов на входе схемы к числу импульсов на выходе старшего разряда.

2. tср (tсрабатывания) – время между поступлением строб-сигнала на С-вход и установлением выходного сигнала в старшем разряде.

, где n- число разрядов.

, где n- число разрядов.

Более выгодным является счетчик с параллельным переносом информации, в котором срабатывание всех триггеров происходит одновременно при поступлении строб-сигналов на все входы.

Составим временную диаграмму работы счетчика.

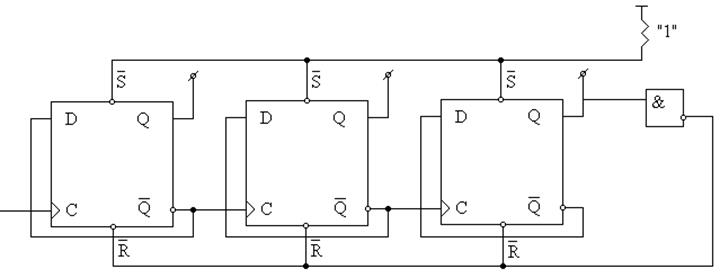

Вычитающий счетчик.

1. Выходной сигнал снимается прямо с инверсного выхода.

2. На счетный вход подают вход прямого выхода.

В вычитающем счетчике на счетный вход последующего триггера сигнал поступает с прямого выхода предыдущего триггера.

При значении  необходимо сбросить счетчик в исходное состояние после поступления заданного количества входных импульсов. Например, пусть заданное

необходимо сбросить счетчик в исходное состояние после поступления заданного количества входных импульсов. Например, пусть заданное  . Операция осуществляется с помощью добавочных элементов и с использованием триггеров с установочными входами. Установочные входы RS имеют приоритетное действие: при поступлении на них сигналов счетчик сбрасывается в исходное состояние.

. Операция осуществляется с помощью добавочных элементов и с использованием триггеров с установочными входами. Установочные входы RS имеют приоритетное действие: при поступлении на них сигналов счетчик сбрасывается в исходное состояние.

Регистры.

Регистр – последовательностная ИС, предназначенная для записи, временного хранения и выдачи цифровой информации и выполнения сдвиговых операций.

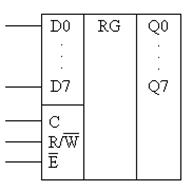

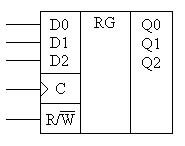

УГО параллельного регистра однофазного по входу и выходу:

Выполняемые операции:

· Запись информации;

· Чтение информации;

· Хранение информации;

· Сдвиг вправо/влево;

· Отчистка.

Все регистры синхронные, т.е. запись и выдача информации производится по сигналу синхронизации на входе CLOCK.

Физическое исполнение:

Физически регистр представляет собой определенным образом соединенный набор триггеров, причем в качестве триггеров применяются RS-, D-, JK-триггеры, но чаще D- триггеры.

D0-D7 – информационные входы;

С – вход синхронизации (разрешение работы);

R/W – чтение/запись информации;

Е – очистка.

Классификация регистров.

- По способу приема и выдачи информации:

1.1. параллельные;

1.2. последовательные;

1.3. универсальные.

- По виду сигналов на входе и выходе (прямые, инверсные):

2.1. парофазные, когда входной и выходной сигнал прямой и инверсный;

2.2. однофазные, когда входной и выходной сигнал либо прямой, либо инверсный.

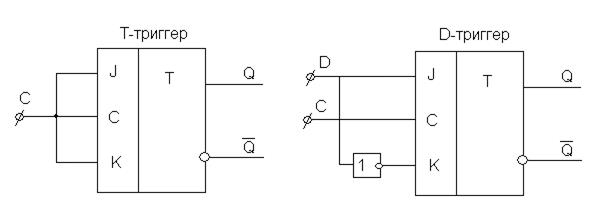

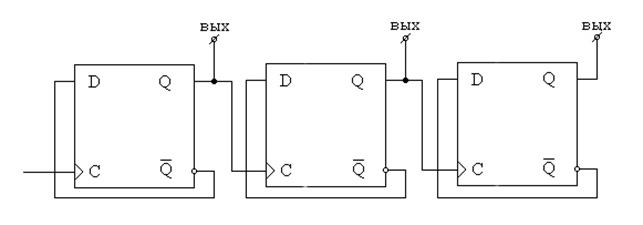

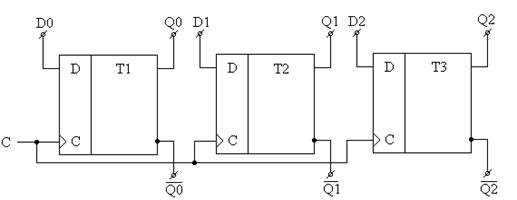

Последовательностный трехразрядный регистр на динамических D-триггерах.

Представлена внутренняя структурная схема последовательностного регистра, однофазного по входу ипарафазного по выходу.

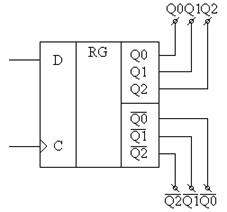

УГО:

| С | D | Q2 | Q1 | Q0 |

| 0->1 | X=1 | 1 | 0 | 0 |

| 0->1 | X=0 | 0 | 1 | 0 |

| 0->1 | X=1 | 1 | 0 | 1 |

Таблица истинности:

При последовательном вводе информации на вход D вводимое слово данных появляется на выходе в параллельном коде, в данном случае, на третьем такте, а в общем случае, такт определяется разрядностью вводимого слова.

Пример: КР155ИР13

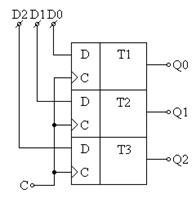

Параллельный трехразрядный регистр на динамических D-триггерах.

УГО:

Параллельный код на входе передается в параллельный код на выходе.

Пример: КР155ИР15

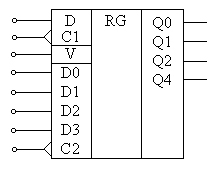

Универсальный регистр.

Данный регистр выполняет следующие операции:

· Если V=1, то схема работает как последовательностный регистр, тогда информация со входа D переписывается на выходы Q0-Q3 при всяком спаде С1 с 1 на 0;

· Если V=0, то схема работает как параллельный регистр, тогда информация со входов D0-D3 переписывается на выходы Q0-Q3 при всяком спаде С2 с 1 на 0.

Пример: КР155ИР1

Область применения:

· Для временного хранения информации во внутренних регистрах МП – сверхоперативная память;

· Как промежуточная область памяти между ЗУ и другими устройствами МП-системы (между шинами, портами вода/вывода).

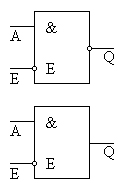

Тристабильные драйверы.

Принцип действия тристабильного драйвера совпадает с принципом действия ЛЭ «Запрет».

УГО:

| E | A | Q | Состояние |

| 1 | 1, 0 | - | 3ье состояние высокого импеданса/сопротивления/х.х |

| 0 | 1 | 1 | Активизация |

| 0 | 0 | 0 | Сброс |

Таблица истинности (для нижней схемы):

Главным в работе тристабильного драйвера является разрешающий работу вход Е (ENABLE). Если на входе Е сигнал соответствующего уровня (в данном случае 0), то схема разрешает передачу информации со входа на выход к устройству, которое подключено к драйверу. Если на входе Е сигнал высокого уровня «1», то схема находится в 3ем состоянии с высоким выходным сопротивлением, иначе говоря, работает в режиме х.х., т.е. отключена от устройства, которому необходимо передать информацию.

Область применения: в шинных формирователях, через которые все устройства МП-системы подключаются к системным шинам. Тот формирователь, который получил сигнал Е, будет общаться с ним через шину.

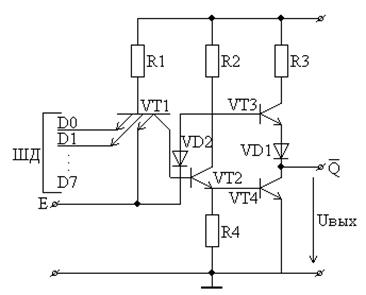

Схемное решение:

Строится на основе базового элемента ТТЛ-логики - И-НЕ, который дополняется вентилями, обеспечивающими подачу сигнала Е. Базовый элемент представляет собой инвертор, но т.к. транзистор VT1 многоэмиттерный, т.е. состояние выхода Q зависит от состояния входов D0-D7, то схема называется И-НЕ.

Добавление диода VD2, подключение его к точке А и соединение с одним из эмиттеров VT1 позволяет или запрещает работу схемы в зависимости от сигнала на входе Е. Сигнал «1» на входе Е приводит к открытию VT2 и VT4, сигнал на выходе – «0». Сигнал «0» на входе Е (даже если D1, D0=0), то работа схемы разрешена и зависит от сигналов на входах D0-D7.

1. Запоминающие устройства.

- Основные определения.

- Технические параметры или показатели памяти.

- Классификация ЗУ.

- Оперативные ЗУ.

5.1. Основные определения.

ЗУ – ИС, предназначенная для хранения команд и операндов. Сама ИС не различает, где код, а где операнд. Для определения местоположения данных памяти ячейкам памяти присвоены неповторяющиеся номера, кот называются адресом.

Адрес – указание места нахождения данных в памяти.

Физически память представляет собой набор однотипных ячеек, регулярно расположенных по строкам и столбцам, т.е. образующих матрицу. Размер каждой ячейки соответствует слову хранения данных.

Словом называется набор бит единиц и нулей, которые записываются или считываются за один машинный код.

Дата: 2019-03-05, просмотров: 406.