ЦИФРОВАЯ ЭЛЕКТРОНИКА.

Получение импульсных электронных сигналов.

- Общая характеристика импульсных режимов.

- Мультивибратор – генератор прямоугольных импульсов.

- Формирование импульсов различной формы.

Общая характеристика импульсных режимов.

Кроме непрерывного сигнала на входе большинства современных электронных устройств используют импульсные сигналы.

Импульсным режимом называют чередование кратковременных сигналов и пауз.

Преимущества импульсных сигналов:

1) импульсный режим позволяет получить при большой мощности импульса – малую среднюю мощность за период, поэтому обеспечивается малая мощность электронного устройства, следовательно, меньше габариты, вес и стоимость;

2) влияние колебаний температуры, невзаимозаменяемости элементной базы на состояние схемы значительно снижено из-за того, что режим работы схемы идет по схеме включена/выключена.

3) сложные электронные устройства (ЭВМ) могут выполняться с помощью большого количества одинаковых электронных элементов, изготовленных по интегральной технологии. Это обеспечивает надежность, малые габариты (вес), малую себестоимость получения всего устройства.

Цифровые сигналы в настоящее время имеют преимущественное распространение перед аналоговыми.

Формы импульсных сигналов.

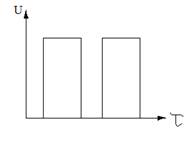

- прямоугольная форма:

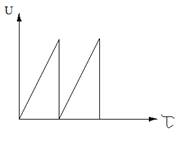

- пилообразная форма:

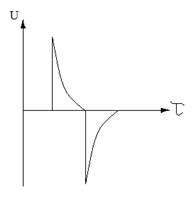

- экспоненциальная форма:

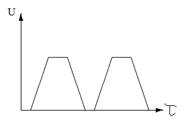

- трапецеидальная форма:

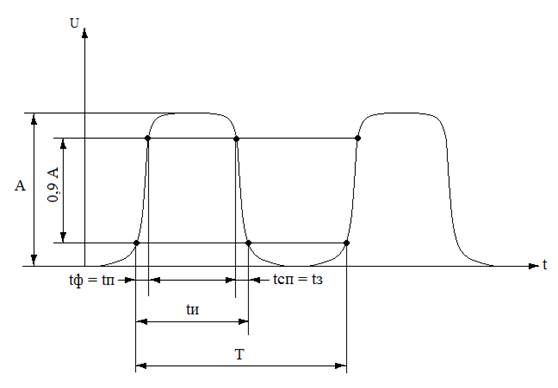

Параметры импульсного сигнала.

А – амплитуда импульса;

Т – период следования импульса;

tи – длительность импульса по основанию;

tф = tя – передний фронт (нарастание импульса);

tсп = tз – время спада импульса (задний фронт);

q – скважность -

10 (скважность радиолокаторов = 10 000).

10 (скважность радиолокаторов = 10 000).

Устройства, обеспечивающие получение импульсных сигналов называют генераторами, а устройства, которые определяют параметры импульса называют формирователями импульса.

Элементная база цифровой электроники.

- Способы представления и передачи цифровой информации.

- Элементарные структуры цифровой электроники.

- Логические элементы.

- Микросхемы комбинационного типа.

- Микросхемы последовательностного типа.

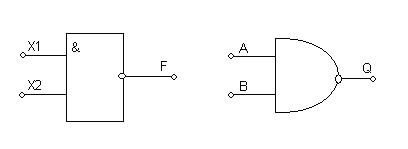

Логические элементы.

Логический элемент – интегральная схема, в которой выходной сигнал связан со входным по законам алгебры логики.

В цифровой электронике в качестве основных логических элементов приняты следующие 7:

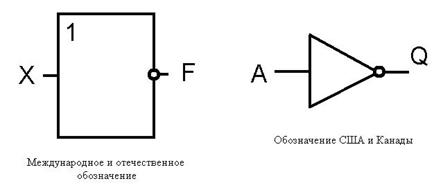

1) НЕ, NOT реализует логическую логическое отрицание (инверсия);

УГО - условное графическое обозначение:

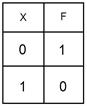

Таблица истинности – сочетание всех возможных выходных сигналов и соответствующих им комбинаций входных сигналов.

ФАЛ - функция алгебры логики:

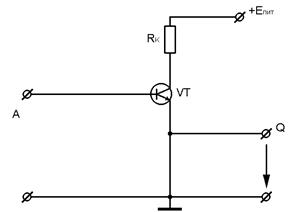

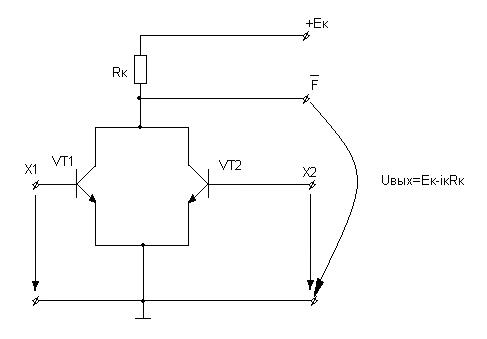

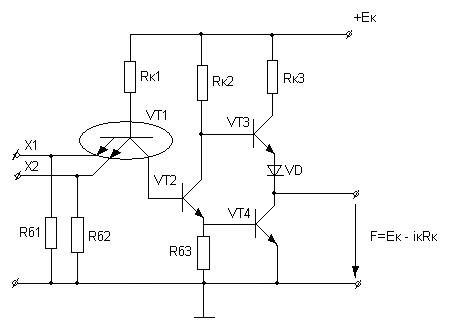

ТТЛ – транзисторно-транзисторная логика:

Транзисторный ключ на биполярном транзисторе может находится в двух состояниях: при наличии входного сигнала транзистор открыт, работает в режиме насыщения, внутреннее сопротивление стремится к 0, а выходное напряжение пропорционально сопротивлению, и ФАЛ равна нулю; а если входной сигнал отсутствует, то транзистор работает в режиме отсечки (закрыт), внутреннее сопротивление стремится к бесконечности, выходной сигнал – напряжение высокого уровня, что соответствует логической единице.

Достоинством этой схемы является быстродействие; недостатком – малая нагрузочная способность.

Под нагрузочной способностью понимают количество устройств, которыми может быть нагружена интегральная схема. Коэффициент разветвления по выходу не более 15.

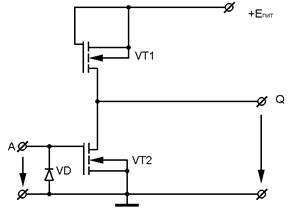

«НЕ» на МОБ-транзисторе.

VT1 выполняет роль коллекторной нагрузки, VT2 – ключа. На затвор VT1 все время подан положительный потенциал, т.е. он всегда открыт; VT2 открыт только в том случае, если на входе есть положительный сигнал, т.е.  =1, внутренне сопротивление равно 0, выходное напряжение равно 0.

=1, внутренне сопротивление равно 0, выходное напряжение равно 0.

К достоинствам относят:

1) на той же площади кристалла, что и у биполярного ключа, располагается в 10 раз больше транзисторов, т.е. стоимость меньше;

2) нагрузочная способность в 10 раз больше, чем на биполярном транзисторе;

3) в 1000 раз меньше потребление мощности от источника питания, поэтому схема распространена. Но быстродействие в 10 раз меньше, это объясняется большими сопротивлениями во входной и выходной цепи и большими входными емкостями конденсатора между затвором и истоком.

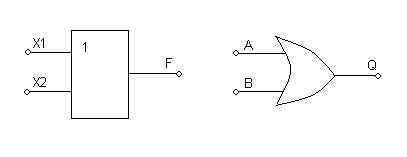

2) ИЛИ, OR реализует логическую функцию – логическое сложение (дизъюнкция);

УГО:

ФАЛ: F = X1 + X2 = X1 V X2.

| X1 | X2 | F |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 1 |

Таблица истинности:

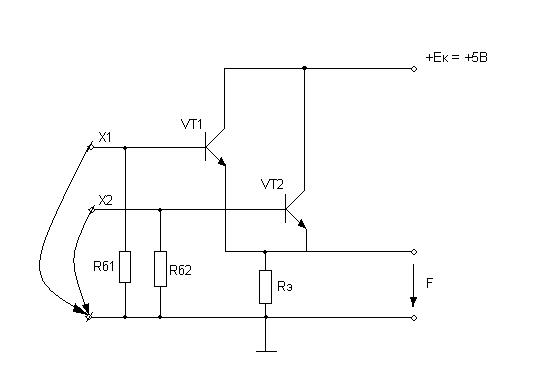

В логике ТТЛ:

Биполярные транзисторы VT1 и VT2 соединены параллельно, входные сигналы подаются на базы транзисторов, выходной – снимается с сопротивления эммитера.

Если хотя бы один транзистор открыт (т.е. сигнал на базе имеет напряжение высокого уровня Х1=Uн=1), то через Rэ проходит ток, который создает падение напряжения на Rэ не равное нулю: F=1=Uн.

Если сигналы на обоих входах отсутствуют, то оба транзистора заперты, токи через них не протекают, напряжение на Rэ равно нулю.

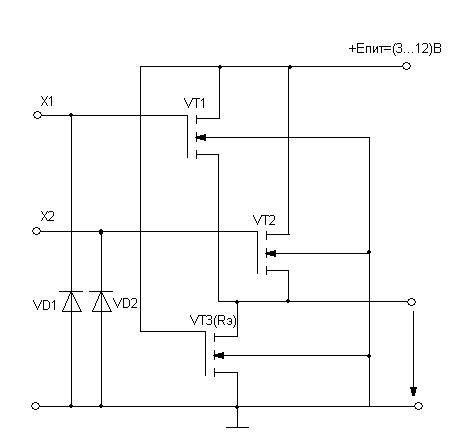

В МДП-логике:

Входные сигналы Х1 и Х2 подаются на затворы VT1 и VT2, в схеме использованы транзисторы с индуцированными каналами. Роль сопротивления нагрузки в этих транзисторах выполняет VT3.

Если на одном из транзисторов VT1/VT2 на затворе положительный потенциал (т.е. 1), то транзистор пропускает ток от +Э, на VT3, который всегда открыт, с VT3 снимаем напряжение.

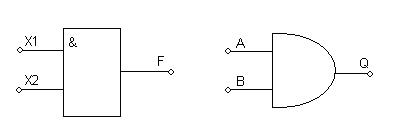

3) И, AND – выполняет функцию логического умножения (конъюнкция).

УГО:

ФАЛ: F = X1*X2 = X1 Λ X2.

| X1 | X2 | F |

| 0 | 0 | 0 |

| 1 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

Таблица истинности:

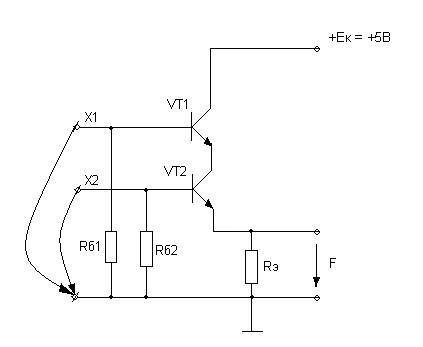

В логике ТТЛ:

В ТТЛ логике биполярные транзисторы VT1 и VT2 теперь соединены последовательно. Напряжение на Rэ появится только в том случае, если будут открыты оба транзистора и VT1 и VT2. Если хоть один из транзисторов закрыт, то сигнал на выходе отсутствует.

Схема И на многоэммитерном транзисторе (с МЭТ VT1):

Отличительной особенностью схемы является использование многоэммитерного транзистора, в котором количествоэммитеров равно количетву входов логического элемента.

Если входные сигналы Х1 и Х2 – напряжение высокого уровня (1), то ток через переходы база-эммитер транзистора VT1 не протекает и вынужден идти через переход база-коллектор, при этом на базе транзистора VT2 появляется отпирающее напряжение, транзистор VT2 открывается, через него протекает ток, который создает на Rэ падение напряжения F=1.

Если хотя бы на 1 из выходов Х1/Х2 сигнал отсутствует, то пойдет ток через переход эммитер-база транзистора VT1 и для включения транзистора VT2, оставшегося тока база-коллектор VT1 будет недостаточно, следовательно, ток через VT2 не протекает F=0.

4) ИЛИ-НЕ, NOR выполняет операцию логического сложения с инверсией.

УГО:

ФАЛ: F =

| X1 | X2 | F |

| 0 | 0 | 1 |

| 1 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 0 |

Таблица истинности:

В логике ТТЛ:

Если на обоих входах транзисторов VT1 и VT2 имеются сигналы, то оба транзистора открыты, протекает ток iк и F  0=0.2

0=0.2  0.3 В.

0.3 В.

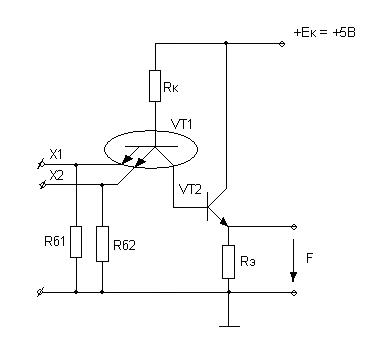

5) И-НЕ, NAND выполняет операцию логического умножения с инверсией.

УГО:

ФАЛ: F=  .

.

| X1 | X2 | F |

| 0 | 0 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

Таблица истинности:

В логике ТТЛ (базовый элемент ТТЛ логики):

Если на входах Х1 и Х2 МЭТ VT1 имеется входное напряжение высокого уровня, то ток через переходы база-эммитер транзистора VT1 не проходит. Весь ток пойдет через переход (VT1) база-коллектор и откроет транзистор VT2, следовательно, потечет ток  , в результате на входе транзистора VT2 низкий потенциал не откроет этот транзистор. С другой стороны появится напряжение на базе транзистора VT4, транзистор VT4 откроется, и тогда на его выходе появится сигнал F=0.

, в результате на входе транзистора VT2 низкий потенциал не откроет этот транзистор. С другой стороны появится напряжение на базе транзистора VT4, транзистор VT4 откроется, и тогда на его выходе появится сигнал F=0.

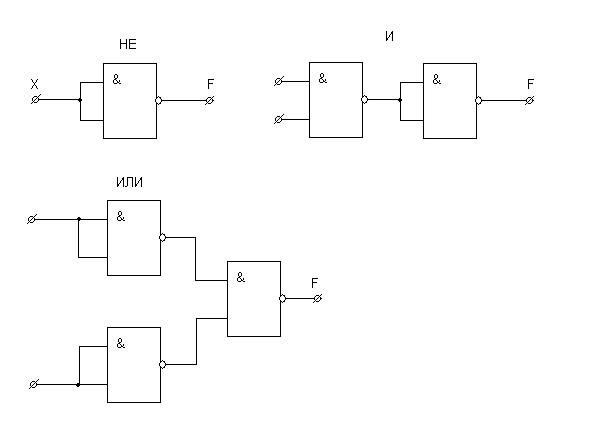

Базовый элемент И-НЕ считается универсальным, т.к. с его помощью можно получить любой логический элемент, в том числе описываемый основными логическими функциями И, ИЛИ, НЕ.

Универсальность базового элемента И-НЕ состоит в том, что, используя только этот элемент, можно создать логическую интегральную схему любой степени сложности.

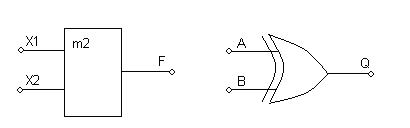

6) ИСКЛЮЧАЮЩЕЕ ИЛИ, XOR – сумматор по модулю 2 или логическая неравнозначность.

УГО:

ФАЛ: F=

| X1 | X2 | F |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

Таблица истинности:

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ может быть получен с использованием:

1) разных логических элементов (НЕ, И-НЕ);

2) в базисе И, НЕ;

3) в базисе ИЛИ, НЕ.

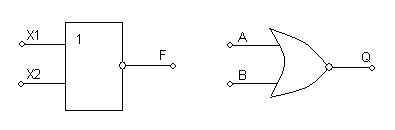

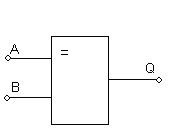

7) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, XNOR – логическая равнозначность.

УГО:

ФАЛ: (А=В)=А*В+

Таблица истинности:

| А | В | А=В | А<В | А>В |

| 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

Сложные логические элементы.

Часто при выполнении функций алгебры логики приходится выполнять последовательность операций И, ИЛИ, НЕ, поэтому промышленность выпускает такие интегральные схемы массовым тиражом.

ИС 555 ЛР 2

2-2-3-4-4И-4ИЛИ-НЕ

Условные обозначения логических элементов:

| К | 1 | 55 | Л | А |

| 1 | 2 | 3 | 4 | 5 |

1) К – широкое применение ИС;

2) 1 – полупроводниковая ИС (технология изготовления ИС);

3) № серии;

4) функциональное назначение (логический элемент)

5) тип логического элемента:

ЛИ – И

ЛН – НЕ

ЛА – И-НЕ

ЛЕ – ИЛИ-НЕ

ЛЛ – ИЛИ

ЛР – И, ИЛИ, НЕ.

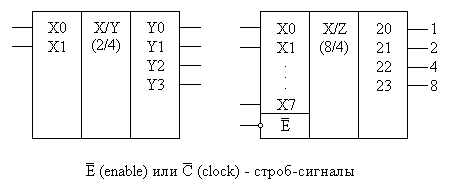

Преобразователи кодов.

Преобразователем кода называется ИС, в которой параллельный m-разрядный цифровой входной сигнал преобразуется параллельный n-разрядный выходной сигнал.

УГО:

Первый преобразователь асинхронный, т.е. сигнал на выходе появляется, как только появляется сигнал на входе. Второй преобразователь синхронный, т.е. сигнал на выходе появляется тогда, когда появляется стробирующий сигнал на входе.

Стробированием называется разрешение.

Во второй схеме разрешающий сигнал – напряжение низкого уровня.

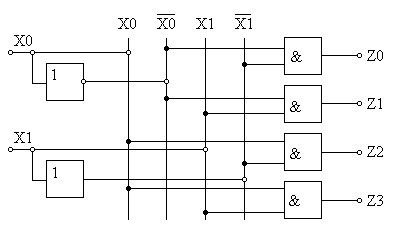

Составим таблицу истинности для X/ Z (2/4):

| Х0 | Х1 | Z3 | Z2 | Z1 | Z0 |

| 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

ФАЛ:

Структурно-логическая схема X/ Z (2/4):

ДДК – это представление любого числа в виде четырехразрядного двоичного (двоично-десятичный код).

Шифраторы и дешифраторы.

Представляют собой частный случай преобразователей кода. В особую группу их выделяют потому, что входной сигнал в шифраторе и выходной сигнал в дешифраторе на одном из входов или выходов равен единице.

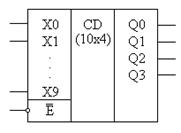

Шифратором называется комбинационная ИС, в которой единичный сигнал на одном из входов преобразуется в ДДК на выходе. Говорят, что шифратор преобразует десятичное входное число МП-системы в ДДК внутренней системы.

УГО:

Таблица истинности:

|

|

| Входы | Выходы | ||||||||||||

| X0 | X1 | X2 | X3 | X4 | X5 | X6 | X7 | X8 | X9 | Q0 | Q1 | Q2 | Q3 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | - | - | - | - | |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 6 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 7 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 8 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 9 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

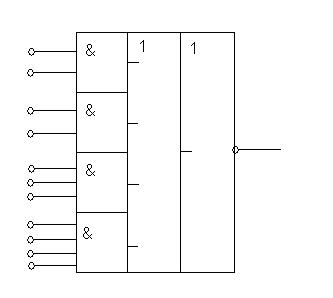

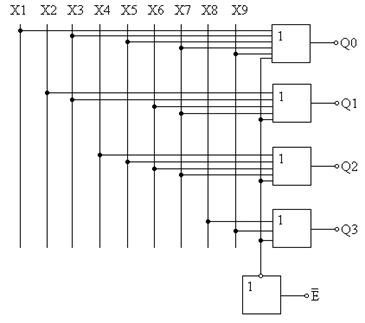

ФАЛ: Q0=X1+X3+X5+X7+X9

Q1=X2+X3+X6+X7

Q2=X4+X5+X6+X7

Q3=X7+X9

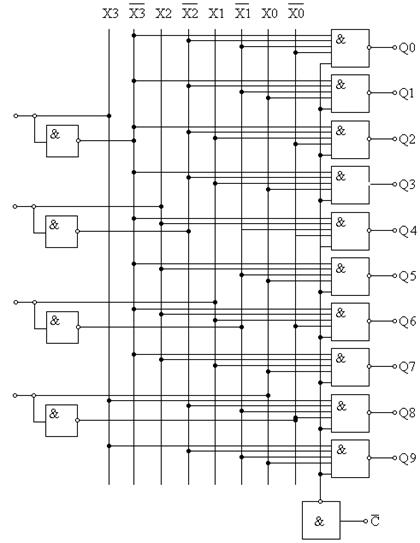

Структурно-логическая схема:

Область применения – для ввода информации с клавиатуры в МП-систему.

Примечание: если количество выходов равно n, то количество входов m равно  , такой шифратор является полным. Если m<

, такой шифратор является полным. Если m<  , то шифратор называется неполным.

, то шифратор называется неполным.

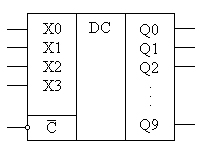

Дешифратором называется комбинационная ИС, в которой ДДК преобразуется единицу на одном из выходов схемы, т.е. в слово команды.

УГО:

Таблица истинности:

| С | Входы | Выходы | ||||||||||||

| Х3 | Х2 | Х1 | Х0 | Q9 | Q8 | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

ФАЛ:

ФАЛ:

Структурно-логическая схема:

Область применения:

l для организации шин адреса требуемой разрядности;

l для включения на выходе МП-системы печатающих и светосигнальных устройств;

l для селекции одного из используемых устройств на выходе МП-системы.

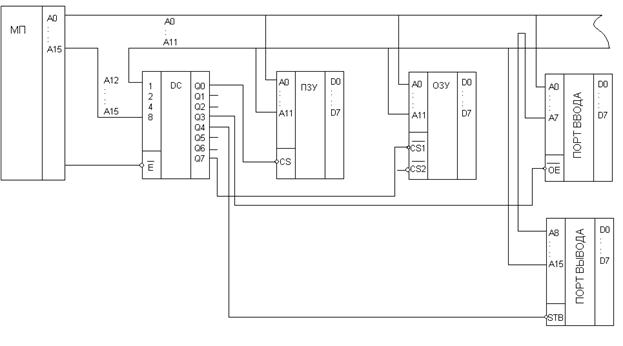

Использование цифровых дешифраторов для выбора адреса устройства МП-системы.

В зависимости от кода сигнала на выходе, напряжение высокого уровня (логическая единица) появляется только на одном выходе. Номер выхода должен соответствовать номеру входа.

Карта памяти:

0000 – 7FFFF – ПЗУ, область монитора;

8000 – 83С6 – ОЗУ, область пользователя.

Выводы декодера Q0-Q7 подключены к выводам ChipSelect(CS)-выбор модуля ВМ, схем памяти.

На вход декодера поступают старшие разряды шины адреса, которые определяют область памяти, с которой собирается общаться МП.

Сигнал высокого уровня на выходе дешифратора соответствует тому номеру, который поступил на его входы. Если в старшем разряде 0, то 1 на Q0, если в старшем разряде 1000, то 1 на Q8.

Соответствующее включение обеспечивает: в первом случае – схема ПЗУ, во втором случае – схема Номер ячейки памяти, из которой считывается информация, определяется уровнем сигналов на остальных проводниках шины адреса.

Таким образом, декодер (дешифратор адреса) осуществляет адресацию памяти.

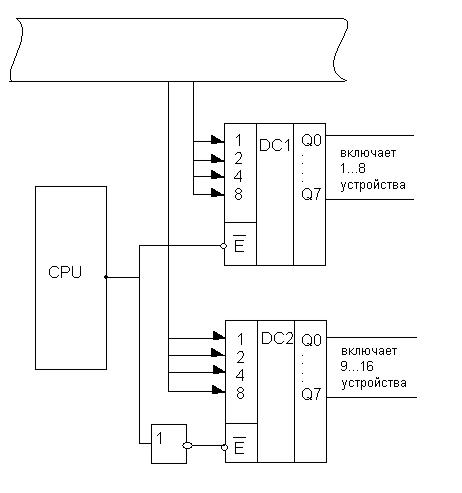

Для увеличения разрядности выходного сигнала декодера, т.е. для подключения большего количества ИС, можно применить 2 декодера (4/10), включенных в так называемую дерево-схему.

Используя дерево-схему декодеров(4/10) можно увеличить количество адресуемых устройств (выбираемых) до 16.

Сумматоры.

Сумматор – комбинационная интегральная схема, предназначенная для выполнения операций сложения двух двоичных чисел в двоично-десятичном или двоичном коде.

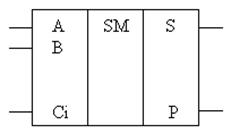

УГО:

А, В – введенная двоичная информация (одноразрядные двоичные числа);

Ci (carry in) – ввод переноса;

S – вывод суммы;

Р (Co – carry out) – вывод переноса/полусуммы.

| A | B | S | P |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Таблица состояний для одноразрядного сумматора:

ФАЛ:

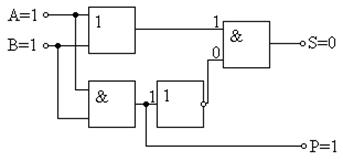

Структурная схема:

Одноразрядный сумматор включает в себя 1 элемент «ИЛИ», 2 – «И» и 1 – «НЕ».

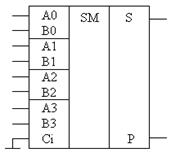

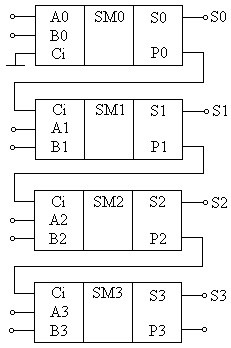

Для построения многоразрядных сумматоров используется набор одноразрядных сумматоров, соединенных определенным образом, причем количество сумматоров равно числу складываемых разрядов. Рассмотрим 4ех-разрядный сумматор – К134ИМ5.

УГО:

При построении сумматоров действует следующий принцип: свободные входы заземлить, а для свободных выходов организовать х.х., т.е. никуда не подключать.

Область применения: в арифметико-логических устройствах, которые могут быть как самостоятельными ИС, так и входными составляющими МП.

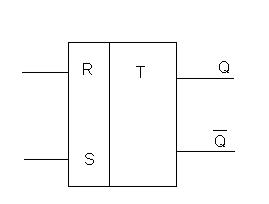

Триггеры.

Триггер – ИС, имеющая два состояния устойчивого равновесия, способная скачком переходить из одного устойчивого состояния в другое под действием внешнего управляющего сигнала.

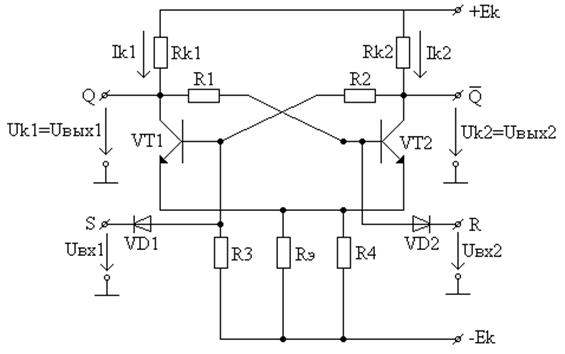

Схемное решение триггеров.

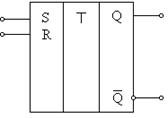

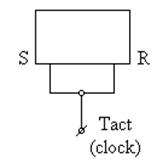

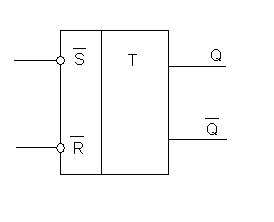

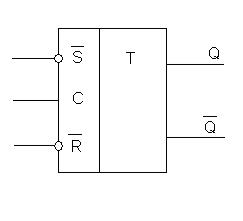

УГО:

Принцип действия:

В основе лежит уравнение Кирхгофа: Uвых=Ек-IкRк. В силу невзаимозаменяемости биполярных транзисторов всегда оказывается, что один из транзисторов открыт чуть больше другого.

Если VT1 открыт больше VT2, то Iк1> Iк2, т.е.  .

.

Процесс идет скачком, пока VT1 полностью открыт, а VT2 полностью закрыт. Это первое условие равновесия триггера. Его внутренняя схема представляет собой 2ух-каскадный УПТ с перекрестными 100%-ными положительными обратными связями R1 и R2. Описанное состояние триггер способен сохранять сколь угодно долгое время, пока на его входы не поступит управляющий сигнал (отрицательный внешний импульс). При поступлении отрицательного импульса на вход SET-установка VT1 скачком закроется, а VT2 откроется, в результате,  . Если подать отрицательный сигнал на вход закрытого транзистора, то его состояние не изменится (на вход RESET-сброс).

. Если подать отрицательный сигнал на вход закрытого транзистора, то его состояние не изменится (на вход RESET-сброс).

Постулат триггера состоит в следующем: на одном выходе триггера должна быть единица, на другом – 0, и наоборот.

Если объединить входы SET и RESET, и подавать входные импульсы сразу на оба входа, то триггер будет изменять свое выходное состояние при поступлении каждого входного импульса. Такой триггер назвали Т-триггером или счетным триггером.

Классификация триггеров.

1. По времени срабатывания:

1.1. Асинхронные триггеры, которые срабатывают в любой момент времени при появлении информации одновременно на обоих информационных входах S и R.

1.2. Синхронные триггеры, которые срабатывают при поступлении строб-сигналов.

1.2.1. Статические триггеры, которые срабатывают при определенном уровне строб-сигнала.

1.2.1.1. Однотактные триггеры.

1.2.1.2. 2ух-тактные триггеры.

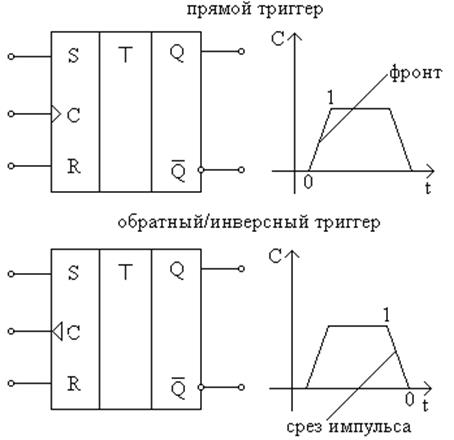

1.2.2. Динамические триггеры, которые срабатывают на фронте или на срезе строб-сигнала.

2. По функциональному назначению:

2.1. RS-триггеры;

2.2. D-триггеры;

2.3. счетные Т-триггеры;

2.4. JK-триггеры или универсальные триггеры.

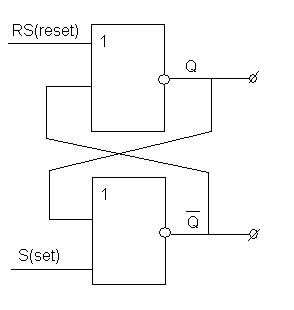

Асинхронные RS-триггеры.

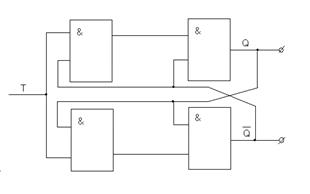

Асинхронные RS-триггеры выполняются или на элементах «ИЛИ-НЕ» или на элементах «И-НЕ», причем во внутренней логической схеме триггера должны присутствовать по 2 логических элемента, охваченных 100%-ми перекрестными обратными связями.

1. ИЛИ-НЕ.

Структурно-логическая схема:

УГО:

Срабатывает при сигналах высокого уровня. Асинхронный RS-триггер имеет 2 информационных входа (set, reset), и 2 выхода (Q,  ).

).

Таблица истинности:

| R | S |

|

|

|

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | ||||

| 0 | 1 | 0 | 0 | 1 | 0 | Активизация (установка единицы) |

| 1 | 0 | 0 | 0 | 0 | 1 | Сброс (установка нуля) |

| 0 | 0 | 0 | 1 | 0 | 1 | Память (предыдущее состояние) |

| 1 | 1 | 0 | 0 | 0 | 0 | Неустойчивое состояние |

Триггер фактически двухтактный, т.к. в момент времени t – информация записывается в триггер, а в момент времени t+1 – переносится на выходы.

Наличие еа выходе триггера активных сигналов для схемы ИЛИ-НЕ, триггер находится в неустойчивом состоянии, поэтому такая комбинация входных сигналов называется запрещенной.

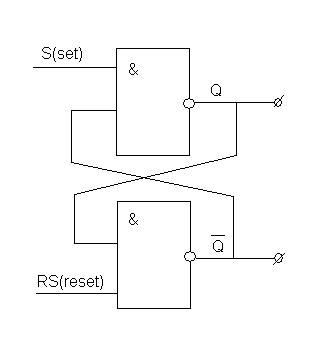

2. И-НЕ.

Структурно-логическая схема:

УГО:

Срабатывает при сигналах низкого уровня.

Таблица истинности:

|

|

|

|

|

| CОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | ||||

| 0 | 1 | 1 | 1 | 1 | 0 | Активизация |

| 1 | 0 | 1 | 1 | 0 | 1 | Сброс |

| 1 | 1 | 0 | 1 | 0 | 1 | Память |

| 0 | 0 | 1 | 1 | 1 | 1 | Неустойчивое состояние |

0,0 – недопустимая комбинация входных сигналов, для триггеров на элементах ИЛИ-НЕ.

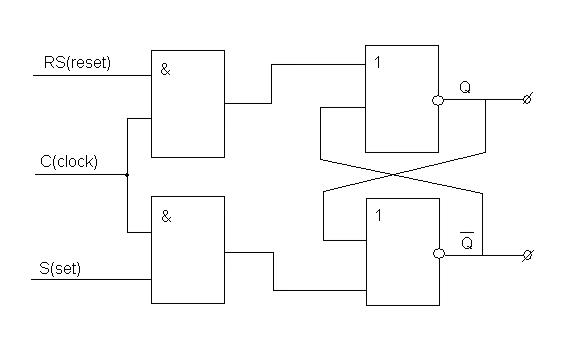

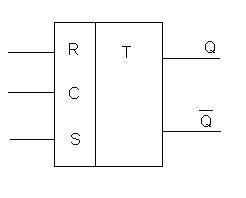

Синхронные RS-триггеры.

1. ИЛИ-НЕ.

Структурно-логическая схема:

УГО:

Таблица состояний:

| C | R | S |

|

|

|

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | |||||

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | Память |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | Активизация |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | Сброс |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | Неустойчивое состояние |

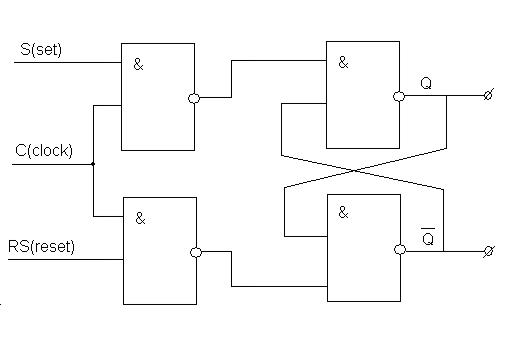

2. И-НЕ.

Структурно-логическая схема:

УГО:

Таблица состояний:

К недостаткам асинхронных и синхронных RS-триггеров относят:

1) наличие запрещенных комбинаций входных сигналов;

2) необходимость подачи сразу двух сигналов: на вход set и на вход reset.

Область применения: только в качестве элементов в ячейках памяти.

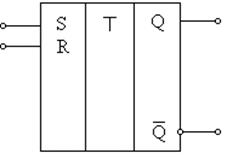

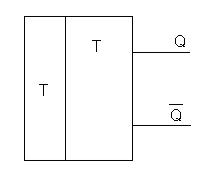

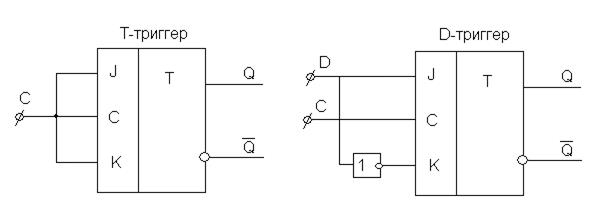

Счетные триггеры или Т-триггеры { T - такт}.

Структурно-логическая схема:

УГО:

Таблица состояний:

| T |

|

|

|

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | |||

| 0 | 0 | 1 | 0 | 1 | Память |

| 1 | 0 | 1 | 1 | 0 | Первый импульс |

| 1 | 0 | 1 | 0 | 1 | Второй импульс |

Счетный триггер меняет состояние своих выходов, при поступлении каждого нового сигнала на вход.

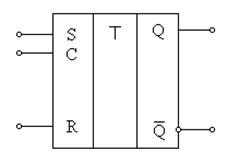

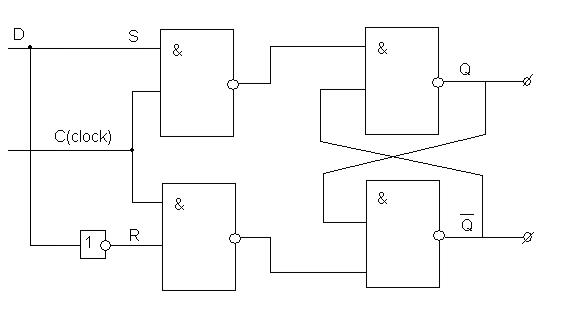

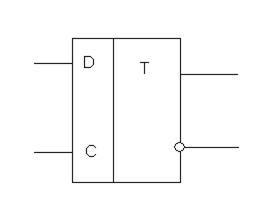

D-триггеры { D – delay – защелка, задержка}.

Структурно-логическая схема:

УГО:

В D-триггере имеется один информационный вход и 1 вход синхронизации (разрешения, стробирования). Одновременная подача на вход S и R противоположных по знаку сигнала, за счет внутреннего инвертирования сигнала D, с помощбю элемента НЕ.

Таблица истинности:

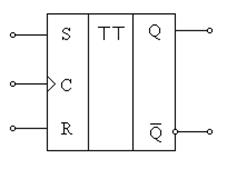

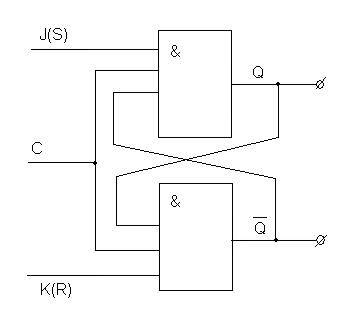

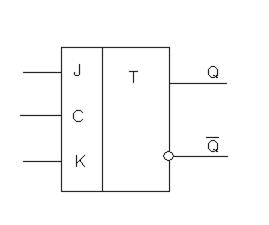

Универсальный JK-триггер{JK – jump keep}.

Структурно-логическая схема:

УГО:

Таблица состояний:

| С | J | R | Q |

| СОСТОЯНИЕ |

| 0 | 1 | Исходное состояние | |||

| 1 | 1 | 1 | 1 | 0 | Режим счета (1 импульс) |

| 1 | 1 | 1 | 0 | 1 | Режим счета |

Для организации режима счета, на входы J и K подаются одинаковые сигналы логической единицы.

Если на С единица, а на J – 1, K – 0, или J – 0, K – 1, то режим данных, причем, если на выходе:

Q – 1,  - 0 – активизация;

- 0 – активизация;

Q – 0,  -1 – сброс.

-1 – сброс.

Триггер называется универсальным, потому что, если все 3 входа соединить, то получаем режим счетчика; если на J подать сигнал от D, а на К, через инвертор, то получаем D-триггер.

Область применения: счетные триггеры применяются для счета команд в МП-системах, для счета адресов, для счета циклов выполняемых команд; D-триггеры применяют в различных регистрах, схемах памяти, при записи и считывании информации.

Счетчики импульсов.

Счетчик – последовательностное цифровое устройство, предназначенное для счета входных сигналов.

Классификация.

1. По направлению счета различных суммирований, которыми каждый входной сигнал вызывает инкремент выходного сигнала:

1.1. Вычитающий уменьшение выходного сигнала – декремент;

1.2. Реверсный, осуществляющий либо инкремент, либо декремент, в зависимости от содержания строб-сигнала.

2. По организации межразрядных связей:

2.1. с последовательным переносом информации между разрядами;

2.2. с параллельным переносом информации между разрядами.

3. В зависимости от коэффициента пересчета (модуль счетчика):

3.1. двоичные à  , где k – число разрядов;

, где k – число разрядов;

3.2. ДДК à  , где k – любое.

, где k – любое.

Физическое осуществление счетчиков.

Счетчики выполняются на триггерах, количество которых является разрядностью передаваемой информации. Триггеры соединены последовательно (прямо или инверсно) со счетным входным последующим переносом.

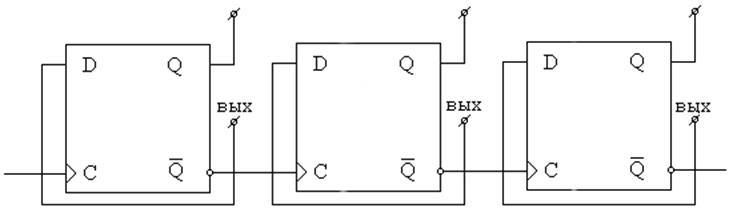

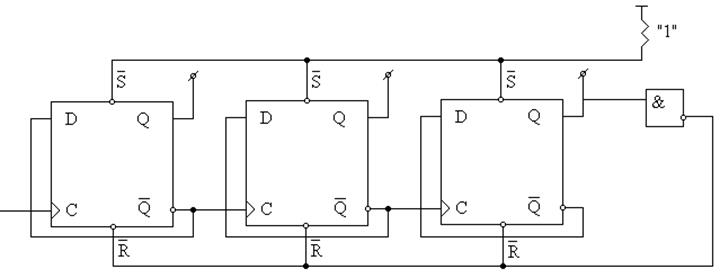

З-ех разрядный суммирующий счетчик с последовательным переносом.

В D-триггере информация со входа D подается на прямой выход. При последовательном переносе осуществляется последовательное срабатывание триггеров. В данном случае D-триггеры прямые динамические, срабатывание осуществляется на входе счетного импульса.

Таблица истинности.

| С | Т1 | Т2 | Т3 | Выходное двоичное слово | Десятичный эквивалент | |||

| Q1 |

| Q2 |

| Q3 |

| |||

| Исходное состояние | 0 | 1 | 0 | 1 | 0 | 1 | 000 | 0 |

| 1ый импульс 0à1 | 1 | 0 | 0 | 1 | 0 | 1 | 001 | 1 |

| 2ой импульс 0à1 | 0 | 1 | 1 | 0 | 0 | 1 | 010 | 2 |

| 3ий импульс 0à1 | 1 | 0 | 1 | 0 | 0 | 1 | 011 | 3 |

| 4ый импульс 0à1 | 0 | 1 | 0 | 1 | 1 | 0 | 100 | 4 |

| 5ый импульс 0à1 | 1 | 0 | 0 | 1 | 1 | 0 | 101 | 5 |

| 6ой импульс 0à1 | 0 | 1 | 1 | 0 | 1 | 0 | 110 | 6 |

| 7ой импульс 0à1 | 1 | 0 | 1 | 0 | 1 | 0 | 111 | 7 |

| 8ой импульс 0à1 | 0 | 1 | 0 | 1 | 0 | 1 | 000 | 0 |

Основные параметры счетчиков.

1. Модуль счета/коэффициент пересчета – количество импульсов, поступающих на вход, после которых внутренняя схема приходит в исходное состояние.

Модуль – отношение числа импульсов на входе схемы к числу импульсов на выходе старшего разряда.

2. tср (tсрабатывания) – время между поступлением строб-сигнала на С-вход и установлением выходного сигнала в старшем разряде.

, где n- число разрядов.

, где n- число разрядов.

Более выгодным является счетчик с параллельным переносом информации, в котором срабатывание всех триггеров происходит одновременно при поступлении строб-сигналов на все входы.

Составим временную диаграмму работы счетчика.

Вычитающий счетчик.

1. Выходной сигнал снимается прямо с инверсного выхода.

2. На счетный вход подают вход прямого выхода.

В вычитающем счетчике на счетный вход последующего триггера сигнал поступает с прямого выхода предыдущего триггера.

При значении  необходимо сбросить счетчик в исходное состояние после поступления заданного количества входных импульсов. Например, пусть заданное

необходимо сбросить счетчик в исходное состояние после поступления заданного количества входных импульсов. Например, пусть заданное  . Операция осуществляется с помощью добавочных элементов и с использованием триггеров с установочными входами. Установочные входы RS имеют приоритетное действие: при поступлении на них сигналов счетчик сбрасывается в исходное состояние.

. Операция осуществляется с помощью добавочных элементов и с использованием триггеров с установочными входами. Установочные входы RS имеют приоритетное действие: при поступлении на них сигналов счетчик сбрасывается в исходное состояние.

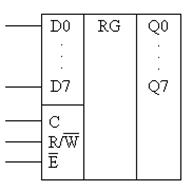

Регистры.

Регистр – последовательностная ИС, предназначенная для записи, временного хранения и выдачи цифровой информации и выполнения сдвиговых операций.

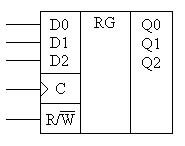

УГО параллельного регистра однофазного по входу и выходу:

Выполняемые операции:

· Запись информации;

· Чтение информации;

· Хранение информации;

· Сдвиг вправо/влево;

· Отчистка.

Все регистры синхронные, т.е. запись и выдача информации производится по сигналу синхронизации на входе CLOCK.

Физическое исполнение:

Физически регистр представляет собой определенным образом соединенный набор триггеров, причем в качестве триггеров применяются RS-, D-, JK-триггеры, но чаще D- триггеры.

D0-D7 – информационные входы;

С – вход синхронизации (разрешение работы);

R/W – чтение/запись информации;

Е – очистка.

Классификация регистров.

- По способу приема и выдачи информации:

1.1. параллельные;

1.2. последовательные;

1.3. универсальные.

- По виду сигналов на входе и выходе (прямые, инверсные):

2.1. парофазные, когда входной и выходной сигнал прямой и инверсный;

2.2. однофазные, когда входной и выходной сигнал либо прямой, либо инверсный.

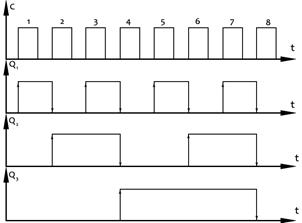

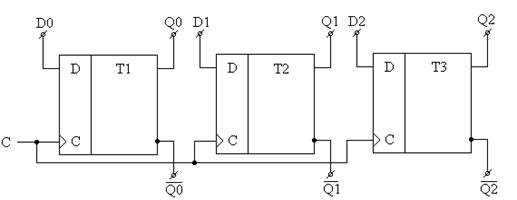

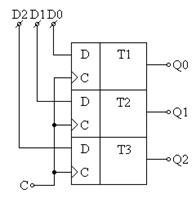

Последовательностный трехразрядный регистр на динамических D-триггерах.

Представлена внутренняя структурная схема последовательностного регистра, однофазного по входу ипарафазного по выходу.

УГО:

| С | D | Q2 | Q1 | Q0 |

| 0->1 | X=1 | 1 | 0 | 0 |

| 0->1 | X=0 | 0 | 1 | 0 |

| 0->1 | X=1 | 1 | 0 | 1 |

Таблица истинности:

При последовательном вводе информации на вход D вводимое слово данных появляется на выходе в параллельном коде, в данном случае, на третьем такте, а в общем случае, такт определяется разрядностью вводимого слова.

Пример: КР155ИР13

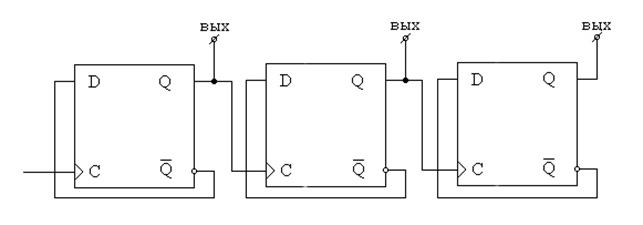

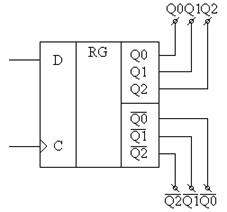

Параллельный трехразрядный регистр на динамических D-триггерах.

УГО:

Параллельный код на входе передается в параллельный код на выходе.

Пример: КР155ИР15

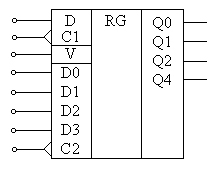

Универсальный регистр.

Данный регистр выполняет следующие операции:

· Если V=1, то схема работает как последовательностный регистр, тогда информация со входа D переписывается на выходы Q0-Q3 при всяком спаде С1 с 1 на 0;

· Если V=0, то схема работает как параллельный регистр, тогда информация со входов D0-D3 переписывается на выходы Q0-Q3 при всяком спаде С2 с 1 на 0.

Пример: КР155ИР1

Область применения:

· Для временного хранения информации во внутренних регистрах МП – сверхоперативная память;

· Как промежуточная область памяти между ЗУ и другими устройствами МП-системы (между шинами, портами вода/вывода).

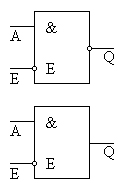

Тристабильные драйверы.

Принцип действия тристабильного драйвера совпадает с принципом действия ЛЭ «Запрет».

УГО:

| E | A | Q | Состояние |

| 1 | 1, 0 | - | 3ье состояние высокого импеданса/сопротивления/х.х |

| 0 | 1 | 1 | Активизация |

| 0 | 0 | 0 | Сброс |

Таблица истинности (для нижней схемы):

Главным в работе тристабильного драйвера является разрешающий работу вход Е (ENABLE). Если на входе Е сигнал соответствующего уровня (в данном случае 0), то схема разрешает передачу информации со входа на выход к устройству, которое подключено к драйверу. Если на входе Е сигнал высокого уровня «1», то схема находится в 3ем состоянии с высоким выходным сопротивлением, иначе говоря, работает в режиме х.х., т.е. отключена от устройства, которому необходимо передать информацию.

Область применения: в шинных формирователях, через которые все устройства МП-системы подключаются к системным шинам. Тот формирователь, который получил сигнал Е, будет общаться с ним через шину.

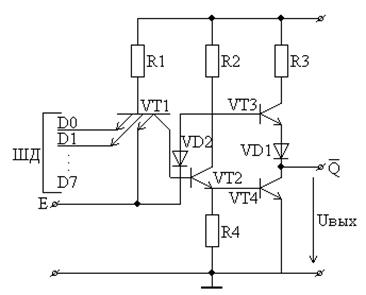

Схемное решение:

Строится на основе базового элемента ТТЛ-логики - И-НЕ, который дополняется вентилями, обеспечивающими подачу сигнала Е. Базовый элемент представляет собой инвертор, но т.к. транзистор VT1 многоэмиттерный, т.е. состояние выхода Q зависит от состояния входов D0-D7, то схема называется И-НЕ.

Добавление диода VD2, подключение его к точке А и соединение с одним из эмиттеров VT1 позволяет или запрещает работу схемы в зависимости от сигнала на входе Е. Сигнал «1» на входе Е приводит к открытию VT2 и VT4, сигнал на выходе – «0». Сигнал «0» на входе Е (даже если D1, D0=0), то работа схемы разрешена и зависит от сигналов на входах D0-D7.

1. Запоминающие устройства.

- Основные определения.

- Технические параметры или показатели памяти.

- Классификация ЗУ.

- Оперативные ЗУ.

5.1. Основные определения.

ЗУ – ИС, предназначенная для хранения команд и операндов. Сама ИС не различает, где код, а где операнд. Для определения местоположения данных памяти ячейкам памяти присвоены неповторяющиеся номера, кот называются адресом.

Адрес – указание места нахождения данных в памяти.

Физически память представляет собой набор однотипных ячеек, регулярно расположенных по строкам и столбцам, т.е. образующих матрицу. Размер каждой ячейки соответствует слову хранения данных.

Словом называется набор бит единиц и нулей, которые записываются или считываются за один машинный код.

Классификация ЗУ.

1. По функциональному назначению:

1.1. внутренние ЗУ – те, которые находятся внутри МП, и, с которыми МП общается через системные шины или внутреннюю ШД.

К ним относят:

· сверхоперативные регистры;

· оперативные ЗУ, предназначенные для хранения команд и данных оператора;

· постоянные ЗУ, предназначенные для хранения программы «монитор», констант и другого, которые записываются на заводе-изготовителе.

1.2. буферные ЗУ – запоминающие устройства для хранения больших объемов информации, к которой МП обращается через порты ввода/вывода.

1.3. внешние ЗУ, которые предназначены для согласования сигналов по уровню, форме (последовательная или параллельная) и по коду. Эти ЗУ входят в состав портов ввода/вывода в виде интерфейсных блоков.

*Интерфейс – ИС сопряжения различных блоков и устройств.

2. По способу доступа к ЗУ:

2.1. ЗУ с произвольным доступом – полупроводниковые ЗУ. Эти схемы позволяют считывать и записывать информацию по любому адресу, не затрагивая предыдущего адреса. Их достоинство – малое время доступа (  =200 нс).

=200 нс).

2.2. ЗУ с последовательным доступом, в котором нужная информация считывается или записывается по указанному адресу только после прохождения всех предыдущих адресов.

Область применения:

· Внутренние ЗУ МП-системы, кроме стека;

· Внешние ЗУ – диски, бобины, флэш-карты.

Оперативные ЗУ.

В зависимости от используемого элемента памяти различают статические и динамические ОЗУ. В статических ОЗУ в качестве элементарной ячейки на 1 бит используется триггер. В динамических ОЗУ в качестве элементарных ячеек памяти используются конденсаторы.

Статические ОЗУ.

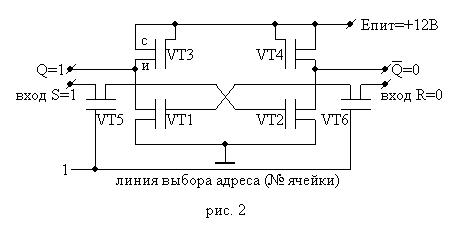

Статические ОЗУ могут выполняться на биполярных транзисторах (рис.1) или на МОП-транзисторах (рис.2).

По линии выбора адреса всегда поступает нулевой сигнал. Если на входе SET тоже 0, то  будет полным, в результате Q=0. Этот потенциал подается на базу VT2, который закрыт, его

будет полным, в результате Q=0. Этот потенциал подается на базу VT2, который закрыт, его  и потенциал на

и потенциал на  . Такое состояние сохраняется до тех пор, пока не поступят новые сигналы на S и R.

. Такое состояние сохраняется до тех пор, пока не поступят новые сигналы на S и R.

Транзисторы VT3 и VT4 выполняют функции нагрузочных регистров  . Транзисторы VT5 и VT6 играют роль входных вентилей – ключей. По линии «выбор адреса ячейки памяти» поступает сигнал логической единицы, тогда VT5 и VT6 открыты. Если S=0 и R=0, то на затвор VT2 подана единица, а на VT1 – 0. VT2 пропускает ток, на его выходе будет 0 (

. Транзисторы VT5 и VT6 играют роль входных вентилей – ключей. По линии «выбор адреса ячейки памяти» поступает сигнал логической единицы, тогда VT5 и VT6 открыты. Если S=0 и R=0, то на затвор VT2 подана единица, а на VT1 – 0. VT2 пропускает ток, на его выходе будет 0 (  ), тогда Q=1.

), тогда Q=1.

Достоинство схемы 1 – высокое быстродействие, поэтому она применяется, когда требуется большая скорость срабатывания. Недостатки – более дорогой технологический способ изготовления или более высокая стоимость такого типа ЗУ.

В схеме 2 вес наоборот, поэтому она более распространена из-за дешевизны. Ее главным достоинством является то, что не требуется никаких блоков регистрации данных для поддержания записанной в памяти информации.

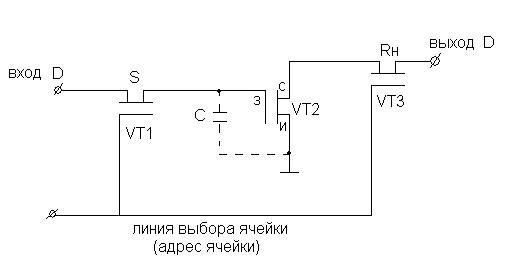

Динамические ОЗУ.

Ячейка динамической ОЗУ на 1 бит (на МОП-транзисторах).

В отличие от статических ОЗУ, у которых запоминающим элементом является триггер на биполярных или полевых транзисторах, у динамических ОЗУ запоминающим элементом является конденсатор, который представляет собой паразитную емкость между затвором и истоком транзистора VT2. Поскольку на затвор подается обратное напряжение порядка 1000 в, то входное сопротивление такого трансформатора представляет величину 10 Мом, что эквивалентно сопротивлению конденсатора. По линии выбора адреса ячейки памяти подается сигнал логической единицы, поэтому затворы VT1, VT3 открывают эти приборы. Транзистор VT1 выполняет функцию включателя, транзистор VT3 – функцию сопротивления нагрузки. При подаче на вход данных в виде логической 1 транзистор VT2 отпирается и паразитная емкость С заряжается до величины этого напряжения, т. е. хранит логическую единицу. Если сигнал на вход не поступает, то С не заряжен и хранит логический нуль. Поскольку VT3 открыт, то логическая единица конденсатора поступает на выход (шина данных).

Достоинства:

- на той же площади кристалла размещается больше бит информации (тут 3 VT, а там 6), следовательно, эти схемы дешевле.

- по сравнению со статическими ОЗУ потребляемая мощность меньше.

Недостатки:

- через сопротивление изоляции между затвором и истоком транзисторов VT1 и VT2 постоянно происходит разряд конденсатора, поэтому с интервалом в 2 мкс необходимо подзаряжать конденсатор, этот процесс называется регенерацией данных.

Динамические ОЗУ для надежного хранения информации требуют дополнительного блока регенерации данных, поэтому если объем динамических ОЗУ маленький, то стоимость блока регенерации «съедает» положительный эффект, который получен размещением большего объема информации. Поэтому динамические ОЗУ применяют: в схемах, хранящих большой объем информации.

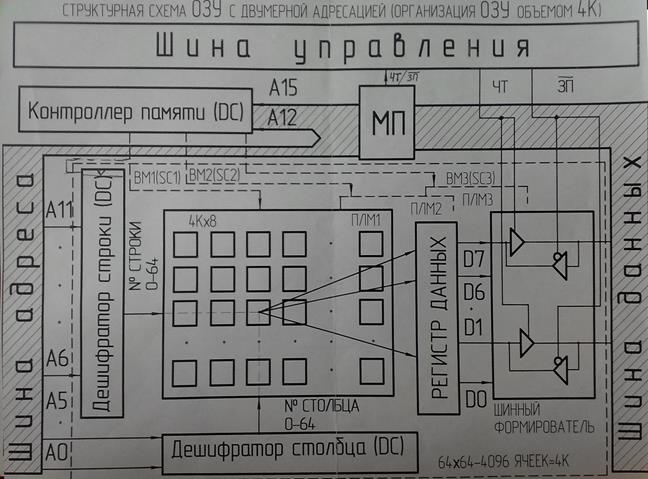

Организация ОЗУ.

Физически ОЗУ состоит из 3х блоков:

1) ПП-матрицы ячеек памяти;

2) дешифратора адреса ячейки;

3) схемы (блока) управления.

Дешифрация адреса выбранной по программе ячейки ОЗУ осуществляется с помощью регистра адреса и 2х декодеров (дешифраторов), определяющих номер строки и номер столбца, на пересечении которых находится нужная ячейка. Распределение адресов происходит следующим образом: старшие байты адреса А12-А15 идут на контроллер памяти, который выдает сигнал выбор модуля CS на выбор соответствующей ИС памяти ПЛМ1, ПЛМ2, … Нумерация адресов в каждой логической матрице одинаковая, информация считывается из ячейки памяти той матрицы, которая получила сигнал выбор модуля – CS. Остальные разряды адреса А0-А11 распределяются между декодерами строк и столбцов – это процесс адресации нужной ячейки памяти.

Процесс считывания или записи данных в ячейку памяти осуществляется с помощью схемы управления каждой ячейки.

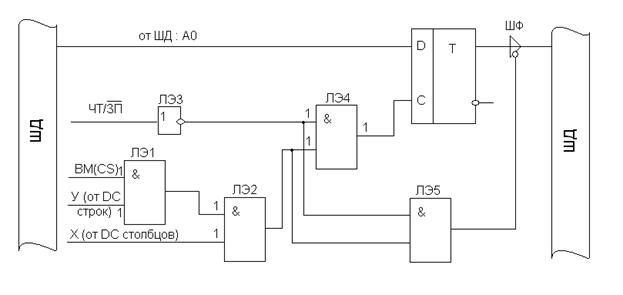

Таблица состояний:

| BM(CS) | ЧТ/ЗП | Состояние |

| 1 | 1 | Чтение из ячейки |

| 1 | 0 | Запись |

| 0 | 1 | Память |

| 0 | 0 |

По поступлении CS высокого уровня, ЛЭ1 (И) срабатывает, возбуждает ЛЭ2, который также срабатывает, результирующий сигнал 1 поступает на один из входов ЛЭ4. Сигнал на втором входе ЛЭ4 зависит от выполняемой операции – чтение/запись. При записи информации в ОЗУ: на входе ЛЭ4 – 1, его схема срабатывает и подает STB-сигнал на D-триггер. В результате данные разряда А0 записываются в триггер. При чтении ячейки ОЗУ: на вход ЛЭ4 поступает 0, 1, на выходе его 0 и триггер не включается (нет STB), зато ЛЭ5 выдает сигнал 0, разрешающий инициализацию формирующую вывод данных из триггера на шину данных.

ПЗУ.

ПЗУ предназначено для постоянного хранения программ и данных. Достоинства перед ОЗУ:

1) меньше потребление мощности;

2) энергонезависимость;

3) хранение большего объема информации.

Классификация в зависимости от способа занесения информации в ПЗУ:

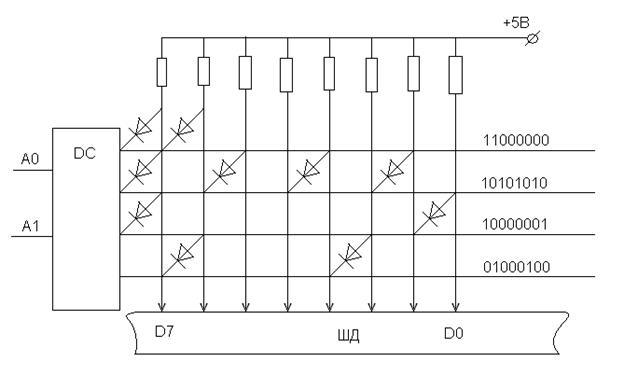

а) стандартные (масочные) ПЗУ. Запись информации в эти ИС производится на заводе изготовителе с помощью шаблонов-масок, т. к. изготовление шаблонов – дорогостоящий процесс, то экономически выгодно применять масочные ПЗУ только в массовом производстве. Примером масочной ПЗУ может служить:

Запись 1/0 – установление связи между шиной адреса и шиной данных. 1 – наличие тока между шиной адреса и шиной данных.

Потребитель не имеет возможности изменить информацию.

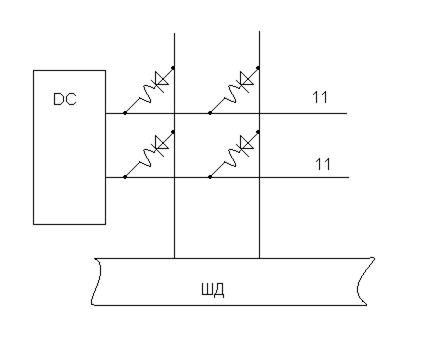

б) перепрограммируемые (ППЗУ) - схемы памяти, допускающие однократное перепрограммирование по желанию заказчика – 1 раз: схемы ПЗУ с пережигаемыми перемычками.

Завод-изготовитель выпускает ИС в которой, в каждой ячейке памяти – 1.

Пережигание перемычек осуществляется импульсами напряжения 10-12 В, и длительностью 100 мс. Эта операция выполняется на специальном программаторе.

в) многократно перепрограммируемые (СППЗУ – стираемые ППЗУ). Эти схемы допускают многократное стирание и запись информации. Стирание выполняется с помощью УФ-излучения через специальное кварцевое окно в ИС с расстояния 10 см в течение 20 мин. Запись осуществляется путем подачи импульсов определенной длительности.

г) электрически перепрограммируемые ПЗУ (ЭППЗУ) допускают многократное стирание и запись информации электрическими импульсами определенной длительности, в течение нескольких мс. Дорогая стоимость обьясняется требованием большого расстояния между соседними ячейками памяти, во избежание их повреждения во время записи/стирания информации.

Организация ПЗУ такая же как у ОЗУ, только легче, т. к. нет сигнала «запись».

ЦИФРОВАЯ ЭЛЕКТРОНИКА.

Получение импульсных электронных сигналов.

- Общая характеристика импульсных режимов.

- Мультивибратор – генератор прямоугольных импульсов.

- Формирование импульсов различной формы.

Дата: 2019-03-05, просмотров: 397.