SR-триггер

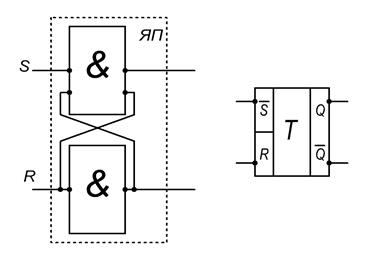

Простейший асинхронный SR-триггер реализуется из двух ячеек И-НЕ (или ИЛИ-НЕ), замкнутых в кольцо, и по существу представляет ЯП без дополнительного. Переключение SR-триггеров, производился сигналом нуль «О», подаваемым на входы S или R . Такие простейшие триггеры входят во все типы более сложных триггеров.

Простейший асинхронный SR-триггер реализуется из двух ячеек И-НЕ (или ИЛИ-НЕ), замкнутых в кольцо, и по существу представляет ЯП без дополнительного. Переключение SR-триггеров, производился сигналом нуль «О», подаваемым на входы S или R . Такие простейшие триггеры входят во все типы более сложных триггеров.

Рис.1 Асинхронный SR-триггер и его условное обозначение.

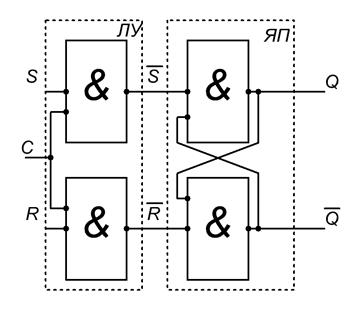

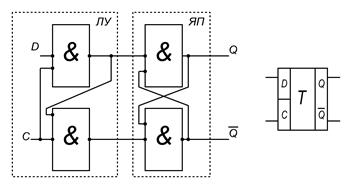

Простейший синхронный SR-триггер содержит кроме ЯП еще ЛУ из двух ячеек И-НЕ. Переключение данного триггера производится сигналом «1», подаваемым на входы S или R и только при наличии синхросигнала С=1.

Простейший синхронный SR-триггер содержит кроме ЯП еще ЛУ из двух ячеек И-НЕ. Переключение данного триггера производится сигналом «1», подаваемым на входы S или R и только при наличии синхросигнала С=1.

Рис.2 Синхронный SR-триггер.

JK-триггер

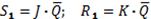

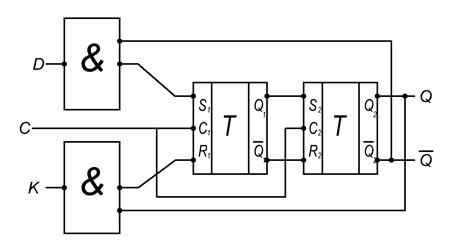

JK-триггер выполняется по двухступенчатой структуре, состоящей из двух синхронных SR-триггеров и двух логических схем И-НЕ. Для данной схемы

.

.

• Если J = 1 и К=0, то при Q=0 получим S1 = 1, и после окончания первого тактового импульса на входе С1 триггер установится в состояние Q = 1.

• Если J = 1 и К = 0, то при Q=1 оба входных сигнала триггера первой ступени S1 = R1 = 0 и, соответственно, весь двухступенчатый триггер не будет изменять своего состояния при приходе синхроимпульсов на вход С.

•  Если же J = K = 1, то получим S1 = 1 и R1 =0 при Q = 0 или S1=0 и Rl = l при Q=1. Вследствие этого триггер переключится в противоположное состояние при соответствующем фронте сигнала на входе С.

Если же J = K = 1, то получим S1 = 1 и R1 =0 при Q = 0 или S1=0 и Rl = l при Q=1. Вследствие этого триггер переключится в противоположное состояние при соответствующем фронте сигнала на входе С.

Рис.3 Логическая схема JK-триггера.

D-триггер

D-триггер

Рис. Логическая схема D-триггера и его условное обозначение.

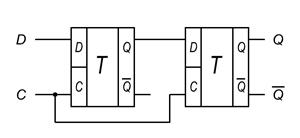

D-триггер состоит из ЯП и ЛУ на двух ячейках И-НЕ. Данный триггер устанавливается в состояние Q=D только при С=1. D-триггер, тактируемый фронтом, построен на двух D-триггерах, тактируемых импульсом.

D-триггер состоит из ЯП и ЛУ на двух ячейках И-НЕ. Данный триггер устанавливается в состояние Q=D только при С=1. D-триггер, тактируемый фронтом, построен на двух D-триггерах, тактируемых импульсом.

Рис.4 D-триггер тактируемый фронтом.

Для данного триггера синхросигнал подается на обе ступени, но в триггере второй ступени он инвертируется. Благодаря этому при любом сигнале на входе С один из двух триггеров не реагирует на сигнал, поступающий на его информационный вход. В результате как при С=0, так и при С=1 изменение сигнала на входе D не приведет к непосредственному изменению выходного сигнала Q. И только в тот момент времени, когда потенциал С переходит 1 в 0, возможно изменение сигнала Q.

При С= 1 триггер первой ступени воспринимает информацию со входа D. Когда же происходит изменение сигнала на входе С и он становится равным 0, производится прием информации триггером второй ступени с выхода триггера.

Т-триггер

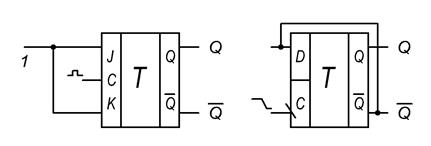

Счётный Т-триггер можно построить на JK-триггере или D-триггере.

Для построения на JK-триггере необходимо сделать J = K = 1 тогда каждый импульс на входе С будет изменять состояние триггера на противоположное, т.е. он стал в Т-триггером.

Рис.5 Счётный Т-триггер на основании JK-триггера и на основе D-триггера.

Для построения счётного Т-триггера на основании D-триггера необходимо сделать

. В такой схеме каждый переход из 1 в 0 импульса на вход С будет приводить к переходу триггера в противоположное состояние.

. В такой схеме каждый переход из 1 в 0 импульса на вход С будет приводить к переходу триггера в противоположное состояние.

Основные параметры интегральных микросхем триггеров.

Основные параметры интегральных микросхем триггеров можно разделить на две группы: статические и динамические.

К статическим параметрам относятся:

• входное напряжение высокого() и низкого уровней(),

• ток потребления от источника питания(Iпот),

• напряжение питания(Uпит),

• нагрузочная способность (Iн – ток отдаваемый в нагрузку),

• потребляемая мощность от источника питания(Рпот).

К динамическим параметрам триггеров относятся:

• время переключения из низкого уровня в высокий(t0-1),

• время переключения из высокого уровня в низкий(t1-0),

• максимальная частота переключения(fmax).

•

Дата: 2018-12-21, просмотров: 392.