Устройство управления (или управляющее устройство) входит в состав микропроцессора и предназначено для подачи управляющих сигналов в устройства ЭВМ, и обеспечивает их соответствующее функционирование и взаимодействие друг с другом.

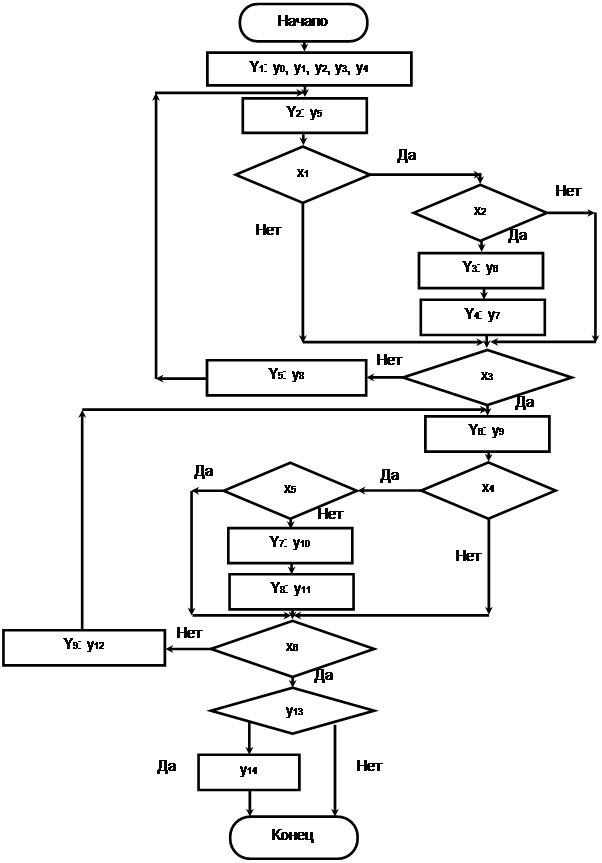

Синтез управляющего устройства основан на синтезе операционного устройства. За основу берётся схема алгоритма операционного устройства, на базе этой схемы строится схема алгоритма в микрооперациях, схема алгоритма в макрооперациях, схема алгоритма в микрокомандах и граф функционирования. Завершающим этапом синтеза устройства управления является построение структурной схемы устройства управления.

Микрооперации обозначаются символами у0, у1, у2 и т. д. Совокупность нескольких однотипных микроопераций образуют макрооперацию. Макрооперации обозначаются символами Y0, Y1, Y2, и т. д. Для обозначения микрокоманд применяются символы а0, а1, а2 и т. д.

|

5.1 Построение схемы алгоритма в микрооперациях

5.1 Построение схемы алгоритма в микрооперациях

|

Построение схемы алгоритма в макрооперациях

| ||||

| ||||

5.3 Построение схемы алгоритма в микрокомандах

5.3 Построение схемы алгоритма в микрокомандах

| ||||

| ||||

Построение графа функционирования

| ||||

| ||||

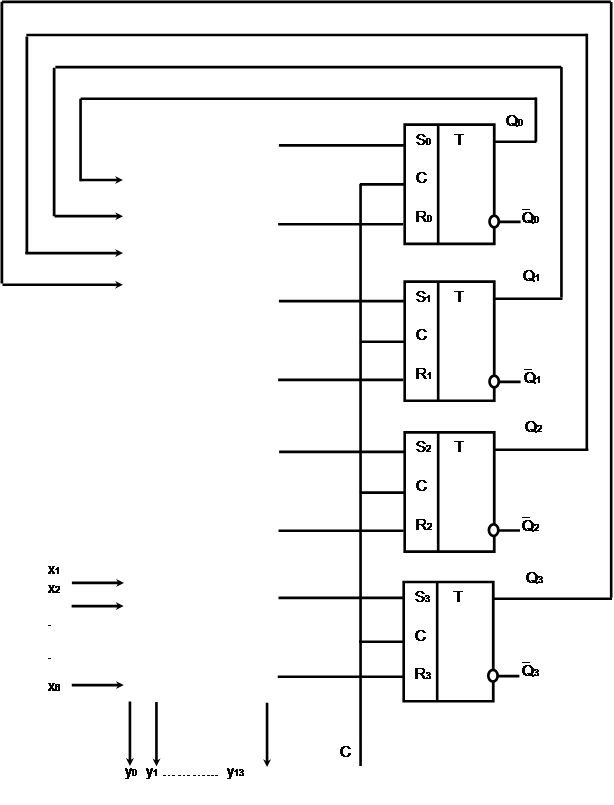

Структурная схема устройства управления

| ||||

| ||||

Цифровые устройства, входящие в состав процессора

Триггеры

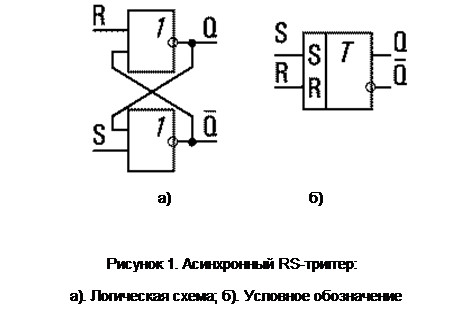

Триггер – это логическая схема, имеющая два устойчивых состояния, которые называются единичным и нулевым и обозначаются 1 и 0.

Триггер предназначен для хранения значения одной логической переменной. В соответствии с этим триггер имеет два состояния: одно из них обозначается как состояние 0, другое – как состояние 1. Воздействуя на входы триггера, его устанавливают в нужное состояние.

Триггер имеет два выхода: прямой Q и инверсный`Q.

Классификация триггеров

1). По типам входов бывают SR-триггеры, JK-триггеры, D-триггеры и Т-триггеры. Эти типы триггеров являются основными.

2). По характеру реакции на входные сигналы триггеры бывают асинхронные и синхронные.

Асинхронные триггеры имеют только информационные (логические) входы. В таком триггере входные сигналы воздействуют на состояние триггера непосредственно с момента их подачи на вход.

Синхронные триггеры имеют дополнительный вход, который обозначается С. Вход С называется дополнительным, управляющим или синхронизирующим. Синхронный триггер срабатывает только при подаче синхронизирующего сигнала на управляющий вход С.

|

Принцип работы триггеров

Каждый тип триггера характеризуется таблицей переходов. Таблица переходов – это форма таблицы истинности, описывающая принцип работы устройства. Обратим внимание на то, что хотя триггер всегда имеет два выхода: прямой Q и инверсный`Q, в таблице переходов принцип работы триггера описывается только при помощи прямого выхода Q.

| Таблица переходов SR-триггера | Таблица переходов JK-триггера | |||||

| S | R | Q | J | K | Q | |

| 0 | 0 | Q0 | 0 | 0 | Q0 | |

| 0 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 1 | * | 1 | 1 | `Q0 | |

|

Вторая таблица переходов соответствует работе JK-триггера. JK-триггер имеет входы установки (J) и сброса (K), подобные входам RS-триггера. В отличие от последнего, допускает одновременную подачу сигналов J и K и при J = К = 1 он устанавливается в состояние, противоположное текущему`Q0. JK-триггер называется универсальным.

Рассмотрим таблицы переходов для D-триггеров и Т-триггеров.

| Таблица переходов D-триггера |

| |||||

| D | Q | Т | Q | |||

| 0 | 0 | 0 | Q0 | |||

| 1 | 1 | 1 | `Q0 | |||

У D-триггера сигналы на выходе такие же, как и на входе. Такой триггер называется информационным.

Т-триггер отличается тем, что если входной сигнал пассивен (т. е. Т = 0), то на выходе сохраняется текущее состояние. Если входной сигнал активен (Т = 1), то на выходе триггер переключается в состояние, противоположное текущему. Такой триггер называют счётным.

|

Асинхронный RS-триггер показан на рисунке 1.

| ||||

| ||||

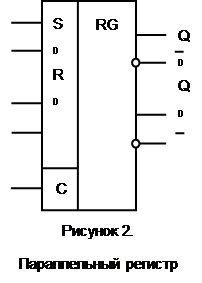

Регистры

Регистр – это цифровое устройство для хранения одного многоразрядного числа.

Регистр является наиболее распространённым узлом цифровой техники и строится в виде набора триггеров, каждый из которых предназначается для хранения цифр определённого числа. Таким образом, регистр для хранения n-разрядного двоичного числа должен содержать n триггеров. Чаще всего регистры строятся на основе синхронных RS-триггеров или D-триггеров. В отдельных случаях регистры могут быть реализованы на базе JK-триггеров.

Классификация регистров:

Поформепредставлениявводимыхчисел регистры бывают:

· параллельные;

·  последовательные.

последовательные.

В параллельный регистр число подаётся одновременно всеми разрядами. Простейший вариант выглядит так: на вход регистра подаётся парафазный код числа, т.е. само число и его инверсия. Очевидно, что необходим триггер, имеющий два входа. Такие регистры обычно строятся на основе простейших синхронных RS-триггеров. Условное обозначение параллельного регистра показано на рисунке 2. Здесь буквами RG показано, что это регистр. Видно, что регистр состоит из двух триггеров, входы первого обозначены S0 и R0, выходы – Q0 и`Q0. Для второго соответственно входы S1 и R1, выходы – Q1 и`Q1. Вход С – это вход сигнала записи (или синхронизирующий, управляющий вход).

|

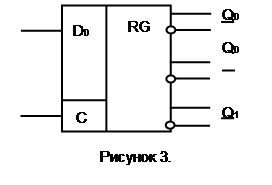

Последовательный регистр отличается от параллельного тем, что число подаётся последовательно, разряд за разрядом. На вход подаётся однофазный код числа (без подачи инверсных значений цифр разрядов), следовательно, RS-триггеры не могут быть использованы, нужны триггеры с одним входом, поэтому обычно применяют D-триггеры. Условное обозначение последовательного трёхразрядного регистра показано на рисунке 3.

Последовательный регистр отличается от параллельного тем, что число подаётся последовательно, разряд за разрядом. На вход подаётся однофазный код числа (без подачи инверсных значений цифр разрядов), следовательно, RS-триггеры не могут быть использованы, нужны триггеры с одним входом, поэтому обычно применяют D-триггеры. Условное обозначение последовательного трёхразрядного регистра показано на рисунке 3.

|

Счётчики

Счётчик – это функциональное устройство, предназначенное для счёта поступающих на его вход сигналов. Счётчики строятся на основе триггеров, следовательно, n-разрядный счётчик содержит n триггеров, при этом количество сигналов, которое может подсчитать счётчик, определяется из выражения N = 2n - 1, где n – число триггеров, а минус один, потому что в цифровой технике за начало отсчёта принимается 0. Таким образом, чтобы подсчитать число элементарных автоматов (триггеров), необходимых для построения счётчика, нужно из формулы выразить n: n = log2N. Классификация счётчиковСчётчики можно классифицировать по следующим признакам:1). По основанию системы счисления счётчики делятся на:а) двоичные;б) десятичные (или двоично-десятичные);Большинство счётчиков работают в двоичном коде, то есть считают от 0 до (2n - 1). Например, 4-х разрядный счётчик будет считать от 0 (код 0000) до 15 (код 1111), а 8-ми разрядный – от 0 (код 0000 0000) до 255 (код 1111 1111). После максимального значения кода счётчик по следующему входному импульсу переключается опять в 0, то есть работает по кругу.

4-х разрядный двоично-десятичный счётчик будет считать от 0 (код 0000) до 9 (код 1001), а 8-ми разрядный двоично-десятичный счётчик будет считать от 0 (код 0000 0000) до 99 (код 1001 1001). Двоично-десятичные счётчики применяются реже обычных двоичных счётчиков.

Принцип работы простейшего 3-х разрядного счётчика показан в таблице 1. Сигнал переноса возникает после появления в счётчике последней комбинации 111 и исчезает при установлении в счётчике состояния 000.

|

Таблица 1 – Таблица состояний 3-х разрядного счётчика

| № | Выходы | |||||

| 02 | 01 | 00 | Перенос | |||

| 0 | 0 | 0 | 0 | |||

| 1 | 0 | 0 | 1 | |||

| 2 | 0 | 1 | 0 | |||

| 3 | 0 | 1 | 1 | |||

| 4 | 1 | 0 | 0 | |||

| 5 | 1 | 0 | 1 | |||

| 6 | 1 | 1 | 0 | |||

| 7 | 1 | 1 | 1 | |||

| 1 | ||||||

| 0 | 0 | 0 | 0 |

| ||

|

Синхронные счётчики характеризуются тем, что все их разряды в пределах одной микросхемы переключаются одновременно, параллельно. Это достигается существенным усложнением внутренней структуры микросхемы по сравнению с простыми асинхронными счётчиками. Синхронные счётчики гораздо быстрее асинхронных. Управление работой синхронного счётчика гораздо сложнее, чем в случае асинхронного счётчика, а количество разрядов синхронных счётчиков обычно не превышает четырех.

|

Шифраторы, дешифраторы

Шифратор или кодер – это логическое устройство, осуществляющее преобразование десятичных чисел в двоичную систему счисления. Классический шифратор имеет m входов и n выходов, при этом между количеством входов и выходов шифратора существует связь: m = 2n. Шифратор с таким количеством входов и выходов называется полным, но используются такие шифраторы достаточно редко, так как в большинстве случаев достаточно меньшего количества входов, т.е. m << 2n.

Шифратор или кодер – это логическое устройство, осуществляющее преобразование десятичных чисел в двоичную систему счисления. Классический шифратор имеет m входов и n выходов, при этом между количеством входов и выходов шифратора существует связь: m = 2n. Шифратор с таким количеством входов и выходов называется полным, но используются такие шифраторы достаточно редко, так как в большинстве случаев достаточно меньшего количества входов, т.е. m << 2n.

Шифраторы используются для преобразования в двоичную систему счисления относительно небольших десятичных чисел. Шифраторы широко используются в разнообразных устройствах ввода информации, например, в клавиатуре, каждая клавиша которой связана с определённым входом шифратора. При нажатии на клавишу подаётся сигнал на соответствующий вход шифратора, и на его выходе возникает двоичное число, соответствующее выгравированному на клавише символу.

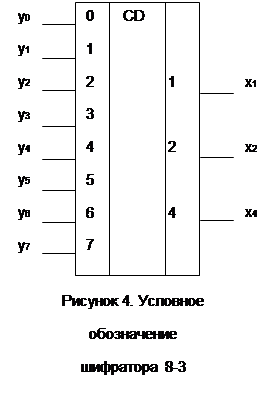

Условное обозначение шифратора показано на рисунке 4. Символ CD образован из букв, входящих в английское слово coder (кодер). Шифратор называется 8-3, так как имеет 8 входов и 3 выхода. Входы показаны слева, они обозначаются десятичными цифрами 0, 1, 2, …, 9, выходы шифратора – справа. Цифрами 1, 2, 4, обозначены весовые коэффициенты двоичных разрядов, соответствующие отдельным выходам.

|

Дешифратором или декодером (decoder) называют кодирующее устройство, преобразующее двоичный код в десятичный. На вход дешифратора подается двоичное число. Сигнал появляется на выходе, номер которого соответствует поданному на вход двоичному числу.

Дешифратором или декодером (decoder) называют кодирующее устройство, преобразующее двоичный код в десятичный. На вход дешифратора подается двоичное число. Сигнал появляется на выходе, номер которого соответствует поданному на вход двоичному числу.

Если декодер имеет n входов, m выходов и использует все возможные наборы входных данных, то m=2n. Такой декодер называется полным. Как и полные шифраторы, полные дешифраторы используются редко, поэтому чаще всего для дешифраторов справедлива формула m << 2n.

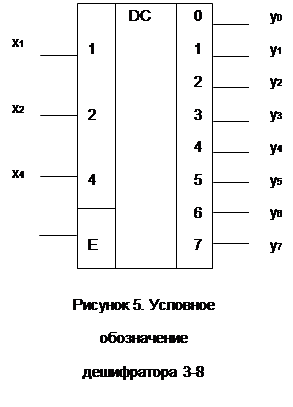

Входы декодера нумеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов 1, 2, 4, 8. Выходы нумеруются десятичными числами, соответствующими отдельным комбинациям входных сигналов. Условное обозначение дешифратора 3-8 (3 входа и 8 выходов) показано на рисунке 5.

Дешифраторы часто имеют разрешающий вход Е (от англ. enable – давать возможность). При Е=1 дешифратор работает как обычно, при Е=0 на всех выходах устанавливаются неактивные уровни независимо от поступившего кода (см. рис. 5). В схемах дешифраторы обозначаются DC.

|

Сумматоры

Сумматор – цифровое устройство, выполняющее операции арифметического сложения над числами.

Если сумматор предназначен для сложения двух входных двоичных кодов, то выходной код будет равен арифметической сумме этих двух входных кодов. Например, если один входной код = 7 (0111), а второй = 5 (0101), то суммарный код на выходе будет = 12 (1100).

При необходимости сумматоры с помощью некоторых вспомогательных операций могут выполнять алгебраическое сложение, вычитание, умножение, деление, сравнение и другие действия с числами.

Классификация сумматоров

Сумматоры классифицируются по следующим признакам:

1). По основанию системы счисления чисел, с которыми оперирует сумматор, сумматоры бывают двоичные, десятичные и двоично-десятичные;

2). По способу обработки многоразрядных чисел сумматоры делят на последовательные и параллельные. В сумматорах последовательного действия цифры какого-либо числа, начиная с младшего разряда, последовательно передаются в канал, обладающий ёмкостью в одну цифру. В сумматорах параллельного действия все цифры числа передаются одновременно, поэтому ёмкость канала должна быть N цифр. В таком устройстве передача всего числа осуществляется за такое же время как у последовательного одна цифра. Сумматоры последовательного действия обладают более низким быстродействием. Суммирование может так же осуществляться параллельно-последовательно и последовательно-параллельно.

3). По количеству обрабатываемых разрядов сумматоры бывают одноразрядные и многоразрядные (2-х, 3-х разрядные и т. д.).

|

Двоичный сумматор

Двоичные сумматоры складывают только двоичные числа. Одноразрядный цифровой двоичный сумматор предназначен для сложения двух двоичных чисел и имеет три входа: два входа слагаемых (обозначаются А и В) и вход переноса С от предыдущего сумматора (от английского carry – перенос). Выходов у одноразрядного двоичного сумматора два: S – выход суммы, Р – выход переноса к следующему сумматору.

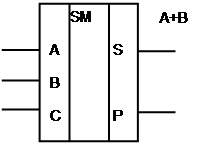

Одноразрядный двоичный сумматор показан на рисунке 6.

Одноразрядный двоичный сумматор показан на рисунке 6.

Рисунок 6 – Одноразрядный двоичный сумматор

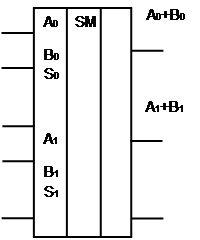

Из одноразрядных сумматоров составляются многоразрядные сумматоры, предназначенные для сложения многоразрядных двоичных чисел. Такой сумматор имеет n входов разрядов слагаемого А, n входов разрядов слагаемого В и вход переноса C. Выходами сумматора являются n выходов разрядов суммы S и выход переноса P (см. рисунок 7).

Из одноразрядных сумматоров составляются многоразрядные сумматоры, предназначенные для сложения многоразрядных двоичных чисел. Такой сумматор имеет n входов разрядов слагаемого А, n входов разрядов слагаемого В и вход переноса C. Выходами сумматора являются n выходов разрядов суммы S и выход переноса P (см. рисунок 7).

|

Компараторы

Компаратор (другое название – схема отношений) – это электронная схема, принимающая на свои входы два аналоговых сигнала и выдающая логический ноль или логическую единицу в зависимости от того, какой из сигналов больше. Компараторы позволяют аппаратурным способом, без выполнения программных операций, сравнивать между собой по качественным отношениям кодовые комбинации. Проще говоря, компараторы сравнивают два входных кода и выдают на выход сигнал о результатах сравнения. На схемах компараторы обозначаются: Comp или двумя символами равенства: = =.

При сравнении чисел кодовые отношения определяются функциями отношений БОЛЬШЕ или МЕНЬШЕ. При равенстве всех разрядов действует кодовое отношение РАВНО.

Функции кодовых отношений обозначаются: F (БОЛЬШЕ), L (МЕНЬШЕ) и В (РАВНО). Отношения определяются на основе последовательного опроса состояний разрядов чисел, начиная со старших разрядов. Способ опроса может быть последовательный, по типу сквозного переноса, или одновременный, по типу группового переноса.

Компараторы строятся на основе логических элементов, например, на так называемых триггерах Шмидта. Триггер Шмидта – не компаратор по своей природе, но устройство с очень схожей областью применения. Другое название этого триггера – несимметричный триггер. Триггер Шмидта стоит особняком в семействе триггеров: он имеет один вход, один выход и не обладает свойствами запоминающего элемента. Такой триггер содержит два последовательно подключенных инвертора, охваченных положительной обратной связью. Простейшая схема триггера Шмидта показана на рисунке 8.

|

|

Рисунок 8 – Триггер Шмидта

В триггере Шмидта переход из одного устойчивого состояния в другое осуществляется при определенных уровнях входного напряжения.

Если на вход триггера Шмидта подавать нарастающее напряжение, то при некотором уровне напряжения в определённый момент времени напряжение на выходе скачком переходит из состояния 0 в состояние 1. Если уменьшать напряжение на входе до некоторого напряжения, то напряжение на выходе скачком переходит из состояния 1 в состояние 0. Таким образом, триггер Шмидта обладает гистерезисным характером.

Рассмотрим схему 4-х разрядного компаратора, сравнивающего величины двух 4-х разрядных чисел. Такой компаратор будет иметь 8 входов: 4 для первого сравниваемого 4-х разрядного числа (обозначаются А0…А3) и 4 – для второго (В0…В3). Кроме того, компаратор имеет три управляющих входа для подачи разрядности (обозначаются А>В, А<В, А=В). Выходов у компаратора три (А>В, А<В, А=В) для выдачи результатов сигналов (см.рис. 9)

Рассмотрим схему 4-х разрядного компаратора, сравнивающего величины двух 4-х разрядных чисел. Такой компаратор будет иметь 8 входов: 4 для первого сравниваемого 4-х разрядного числа (обозначаются А0…А3) и 4 – для второго (В0…В3). Кроме того, компаратор имеет три управляющих входа для подачи разрядности (обозначаются А>В, А<В, А=В). Выходов у компаратора три (А>В, А<В, А=В) для выдачи результатов сигналов (см.рис. 9)

|

Дата: 2019-12-22, просмотров: 320.