Основными элементами структуры ПЛИС семейства MAX3000 являются:

· логические блоки (ЛБ, LAB, Logic Array Blocks);

· макроячейки (МЯ, macrocells);

· логические расширители (expanders), параллельный (parallel) и разделяемый (shareable);

· программируемая матрица соединений (ПМС, Programmable Interconnect Array, PIA);

· элементы ввода/вывода (ЭВВ, I/Ocontrol block).

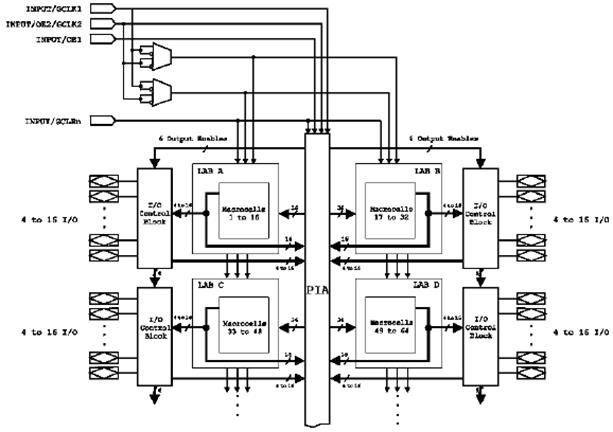

Рис 2.1.1 Функциональная схема ПЛИС семейства MAX3000

ПЛИС семейства MAX3000 имеют четыре вывода, закрепленных за глобальными цепями (dedicated inputs). Это глобальные цепи синхронизации сброса и установки в третье состояние каждой макроячейки. Кроме того, эти выводы можно использовать как входы или выходы пользователя для «быстрых» сигналов, обрабатываемых в ПЛИС.

Как видно из рис 2.1.1, в основе архитектуры ПЛИС семейства МАХ3000 лежат логические блоки, состоящие из 16 макроячеек каждый. Логические блоки соединяются с помощью программируемой матрицы соединений (ПМС). Каждый логический блок имеет 36 входов с ПМС.

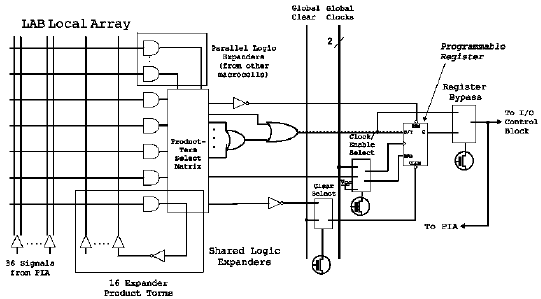

На рис 2.1.2 приведена структурная схема макроячейки ПЛИС семейства MAX3000. Макроячейка ПЛИС семейства MAX3000 состоит из трех основных узлов:

· локальной программируемой матрицы (LAB local array);

· матрицы распределения термов(product-term select matrix);

· программируемого регистра (programmable register).

Комбинационные функции реализуются на локальной программируемой матрице и матрице распределения термов, позволяющей объединять логические произведения либо по ИЛИ (OR), либо по исключающему ИЛИ (XOR). Кроме того, матрица распределения термов позволяет скоммутировать цепи управления триггером макроячейки.

Режим тактирования и конфигурация триггера выбираются автоматически во время синтеза проекта в САПР Max+Plus II в зависимости от выбранного разработчиком типа триггера при описании проекта.

В ПЛИС семейства MAX 3000 доступно 2 глобальных тактовых сигнала, что позволяет проектировать схемы с двухфазной синхронизацией.

Для реализации логических функций большого числа переменных используются логические расширители.

Рис 2.1.2 Структурная схема макроячейки ПЛИС

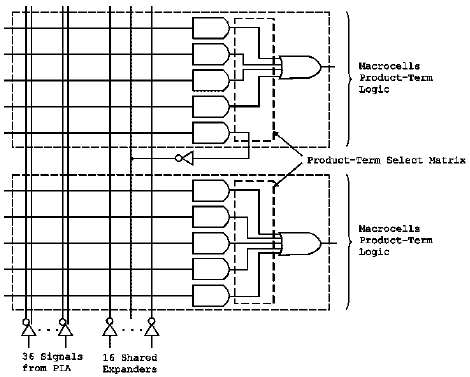

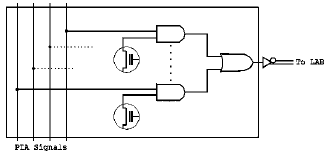

Разделяемый логический расширитель (рис.2.1.3) позволяет реализовать логическую функцию с большим числом входов, предоставляя возможность объединить макроячейки, входящие в состав одного логического блока. Таким образом, разделяемый расширитель формирует терм, инверсное значение которого передается матрицей распределения термов в локальную программируемую матрицу и может быть использовано в любой макроячейки данного логического блока. Как видно из рис.2.1.3, имеется 36 сигналов локальной ПМС, а также 16 инверсных сигналов с разделяемых логических расширителей, что позволяет в пределах одного логического блока реализовать функцию до 52 термов ранга 1.

Рис 2.1.3 Разделяемый логический расширитель

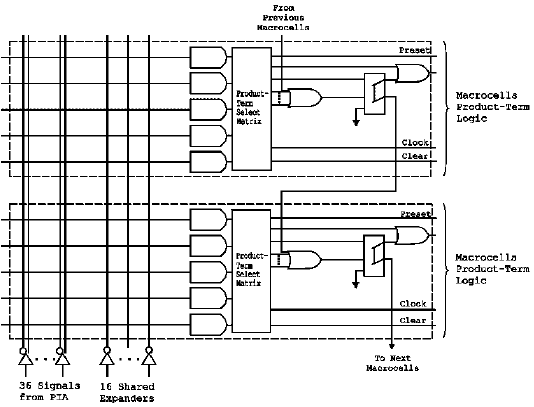

Параллельный логический расширитель (рис. 2.1.4) позволяет использовать локальные матрицы смежных макроячеек для реализации функций, в которые входят более 5 термов. Одна цепочка параллельных расширителей может включать до 4 макроячейки, реализуя функцию 20 термов. Компилятор системы Max+Plus II поддерживает размещение до 3-х наборов не более 5 параллельных расширителей в каждом.

Рис 2.1.4 Параллельный логический расширитель

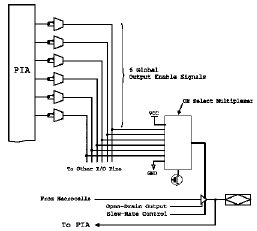

На рис. 2.1.5 приведена структура программируемой матрицы соединений.

На ПМС выводятся сигналы от всех возможных источников: элементов ввода-вывода, сигналов обратной связи логического блока, специализированных выделенных выводов. В процессе программирования только необходимые сигналы «заводятся» на каждый логический блок.

Рис 2.1.5 Структура ПМС ПЛИС семейства МАХ3000

На рис 2.1.6 приведена схема элемента ввода-вывода (ЭВВ) ПЛИС семейства MAX3000. ЭВВ позволяет организовать режимы работы с открытым коллектором и третьим состоянием.

Рис 2.1.6 Элемент ввода вывода

Выберем микросхему ПЛИС семейства MAX3000 – EPM3265ACT144. Данная микросхема является недорогой, содержит достаточное количество макроячеек (256), удовлетворяет параметрам по быстродействию (максимум 156 МГц). Единственная сложность, микросхема имеет большое количество выводов при маленькой площади, что существенно усложняет ее монтаж [3][4].

Компаратор

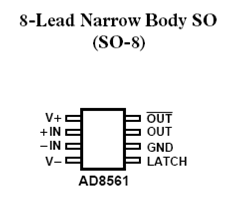

Компаратор сравнивает сигнал с опорным напряжением и оставляет только импульсы с заданной амплитудой. Выходной сигнал компаратора должен быть в виде TTL уровня. В соответствии с заданными характеристиками был выбран компаратор фирмы Analog Devices AD8561.

Рис 2.2.1 Расположение выводов компаратора

Таблица 2.2.1 Общее техническое описание V+ = +5.0 V, V– = VGND = 0 V, TA = +25 C

| Параметры | Обозначения | Условия эксплуатации | min | max | Единицы измерения | |

| Входная емкость | CIN |

| 3 | пФ | ||

| Диапазон входных напряжений | VCM |

| 0 | 3.0 | В | |

| Длительность импульса | tPW(E) |

| 6 | нс | ||

| время срабатывания | ts | 1 | нс | |||

| время удержания | tH | 1.2 | нс | |||

| Цифровой выход (по напряжению) | ||||||

| Логическая “1” | VOH |

| 3.5 | V+ | В | |

| Логический “0” | VOL |

| 0.25 | 0.4 | В | |

| Динамические характеристики | ||||||

| задержка распространения | tP | Продолжительность 200 mV с шагом 100 mV –40C TA +85 | 6.7 | 13 | нс | |

| Питание | ||||||

| Ток источника питания(положительный) | I+ | –40C TA +85C

| 4.5 | 6.0 | мА | |

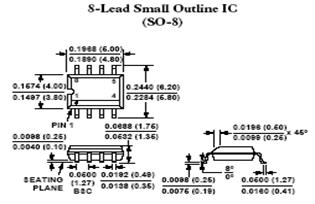

Рис 2.2.2(Физические параметры)

Перед компаратором необходимо поставить делитель, для обеспечения согласования по напряжению и сопротивлению [5].

Генератор тактовой частоты

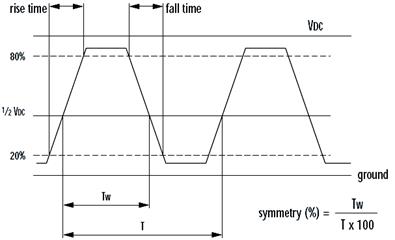

Генератор тактовой частоты необходим для задания временного масштаба счетного устройства на ПЛИС. По тактам генератора будет работать счетное устройство. Был выбран генератор фирмы Auch JCO series с высотой импульсов 5В для CMOS и TTL логики.*

Таблица 2.3.1 Общее техническое описание:

| Частота | 20.0 МГц |

| Ток потребления | 25 мА |

| Стабильность частоты | ± 100 ppm (A-type)* |

| Емкость нагрузки | 50 пФ или 10 TTL |

| Максимальное время спада и подъема | 6 нс |

| Уровень выходного сигнала максимально низкого (лог. «0») | 0.4 В |

| Уровень выходного сигнала минимально высокого(лог. «1») | VDC - 0.5 В |

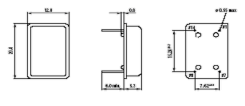

Рис 2.3.1 (Физические параметры)

Рис 2.3.2 (Форма выдаваемого сигнала)

Индикатор

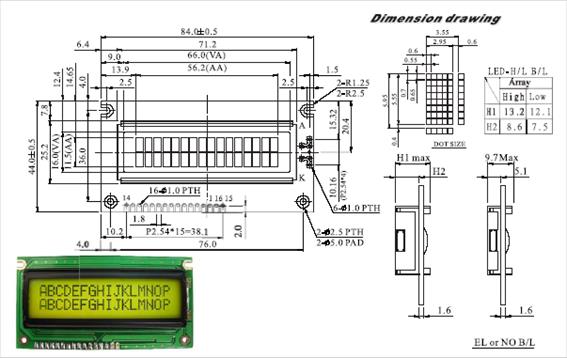

Был выбран двух строчный индикатор WH1602A с внутренней видео памятью и контролером HD44780.

Рис 2.4.1(Внешний вид и габариты индикаторы)

Дата: 2019-12-22, просмотров: 424.