Определение данных с типом структуры имеет следующий вид:

[имя переменной] имя_структуры <[список значений]>

3. Организовать обращение к элементам структуры.

Для того чтобы сослаться в команде на поле некоторой структуры, используется следующее выражение:

имя_переменной.имя_поля_структуры ,

Фрагмент программы. Найти из списка студентов отличника по всем предметам.

Model small

.586p

Stud struc

Name db 20 dup (‘’)

Phisika db ?

Matem db ?

Stud ends

.data

Bufer Stud <””,’’,’’,’’> ;зарезервировали пустую структуру

S1 Stud <”Ivanov”,’5’,’5’,’5’>

S2 Stud <”Petrov”,’3’,’3’,’3’>

S3 Stud <”Сидоров”,’5’,’2’,’5’>

…

mov bx, offset s1

mov al, [bx].Phisika

cmp al, ‘5’

jne m2

mov al, [bx].Matem

cmp al, ‘5’

jne m2

;нашли одного из отличников, надо вывести его фамилию

m2: mov al, s2.Phisika ;ищем следующего отличника

mov ah, s2.Matem

cmp ax, ‘55’

jne m3

;нашли одного из отличников, надо вывести его фамилию

m3: ;ищем следующего отличника

Объединение - тип данных, позволяющий трактовать одну и ту же область памяти как имеющую разные типы и имена.

Описание объединений в программе напоминает описание структур, то есть сначала описывается шаблон, в котором с помощью директив описания данных перечисляются имена и типы полей:

имя_объединения UNION

<описание полей>

имя_объединения ENDS

Отличие объединений от структур состоит, в частности, в том, что при определении переменной типа объединения память выделяется в соответствии с размером максимального элемента. Обращение к элементам объединения происходит по их именам, но при этом нужно, конечно, помнить о том, что все поля в объединении накладываются друг на друга.

Одновременная работа с элементами объединения исключена. В качестве элементов объединения можно использовать и структуры.

Model small

.586p

st union

stu1 dw ?

stu2 db ?

stu3 dd ?

st ends

.data

q st <> ;пустое объединение

z st <12ffh> ;заполнили объединение значением

…

mov q.stu2, al ;в переменную положили содержимое регистра al

mov q.stu3, edx

mov bx, z.stu1

mov dx, offset q.stu1

Запись - структурный тип данных, состоящий из фиксированного числа элементов длиной от одного до нескольких бит. При описании записи для каждого элемента указывается его длина в битах и, что необязательно, некоторое значение. Суммарный размер записи определяется суммой размеров ее полей и не может быть более 8, 16 или 32 бит. Если суммарный размер записи меньше указанных значений, то все поля записи “прижимаются” к младшим разрядам

Использование записей в программе, так же, как и структур, организуется в три этапа:

1. Описание шаблона записи

имя_записи RECORD <описание элементов>

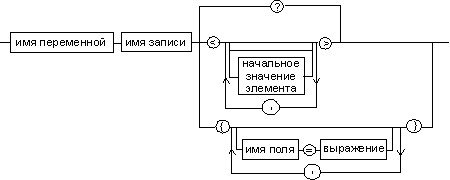

2. Для использования шаблона записи в программе необходимо определить переменную с типом данной записи, для чего применяется следующая синтаксическая конструкция (рис. 7):

3. Организация работы с записями. Обычные механизмы адресации бессильны, поскольку они работают на уровне байтов, а не отдельных битов.

- каждому имени элемента записи ассемблер присваивает числовое значение, равное количеству сдвигов вправо, которое нужно произвести, для того чтобы этот элемент оказался прижатым к началу ячейки памяти;

- размер элемента записи в битах можно узнать с помощью оператора width;

- оператор mask позволяет локализовать биты нужного элемента записи;

- все действия по преобразованию элементов записи производятся с помощью логических команд;

- команда setfield устанавливает значение некоторого поля записи

setfield имя_элемента_записи регистр_ назначение, регистр_источник

- команда getfield осуществляет выборку некоторого поля записи

getfield имя_элемента_записи регистр_назначение, регистр_ источник

Процедуры. Макрокоманды

Процедура, часто называемая подпрограммой, - это правильным образом оформленная совокупность команд, которая будучи однократно описана, при необходимости может быть вызвана в любом месте программы. Процедура представляет собой группу команд для решения конкретной подзадачи и обладает средствами получения управления из точки вызова задачи более высокого уровня и возврата управления в эту точку. В простейшем случае программа может состоять из одной процедуры.

Описание процедуры может размещается в любом месте программы, но таким образом чтобы на нее случайным образом не попало управление:

- в начале программы, до первой исполняемой команды;

- в конце, после команды возвращающей управление операционной системе;

- промежуточный вариант, тело процедуры располагается внутри другой процедуры или основной программы. В этом случае необходимо предусмотреть обход процедуры командой jmp;

- в другом модуле.

Синтаксис описания процедуры:

Имя_процедуры PROC заголовок

Команды, директивы тело процедуры

[ ret ] возврат из процедуры

[имя_процедуры] ENDP конец процедуры

Вызов процедуры осуществляется командой

CALL [модификатор] имя_процедуры

Команда call передает управление по адресу с символическим адресом имя_процедуры, с сохранением в стеке адреса возврата, команды следующей после команды call.

Возврат из процедуры осуществляется по команде

RET [число]

Команда ret считывает адрес возврата из стека и загружает его в регистры cs и ip/eip, возвращая таким образом управление команде, следующей за командой call. Число – необязательный параметр, обозначающий количество элементов, удаляемых из стека при возврате из процедуры. Размер элемента зависит от используемой модели сегментации 32 или 16 разрядной.

Передача аргументов из/в процедуру может осуществляться через регистры, переменные или стек.

Пример .

| Model small .stack 100h .data w db 25 dup (?) .code vvod proc mov ah, 0ah lea dx, w int 21h ret vvod endp main: | … Call schet Call vvod … exit: mov ax,4c00h int 21h schet proc .. ret schet endp end main |

Макрокоманда является одним из многих механизмов замены текста программы. С помощью макрокоманды в текст программы можно вставлять последовательности строк и привязывать их к месту вставки.

Макрокоманда представляет собой строку, содержащую некоторое имя – имя макрокоманды, предназначенное для того, чтобы быть замещенным одной или несколькими другими строками при трансляции.

Для работы с макрокомандой вначале необходимо задать ее шаблон-описание, так называемое макроопределение.

Имя_макрокоманды MACRO [список_формальных_аргументов]

<Тело макроопределения>

ENDM

Существует три варианта расположения макроопределений:

- в начале исходного текста программы до сегмента кода и данных с тем, чтобы не ухудшать читабельность программы. В данном случае макрокоманды будут актуальны только в пределах этой программы;

- в отдельном файле. Для того, чтобы использовать эти макроопределения в других программах, необходимо в начале исходного текста этих программ записать директиву

include имя_файла

- в макробиблиотеке. Макробиблиотека создается в том случае, когда написанные макросы используются практически во всех программах. Подключается библиотека директивой include. Недостаток этого и предыдущего методов в том, что в исходный текст программы включаются абсолютно все макроопределения. Для исправления ситуации можно использовать директиву purge, в качестве операндов которой перечисляются макрокоманды, которые не должны включаться в текст программы.

Include macrobibl.inc ;в исходный текст программы будут вставлены строки из macrobibl.inc

Purge outstr, exit ;за исключением макроопределений outstr, exit

Активизация макроса осуществляется следующим образом:

Имя_макрокоманды список_ фактических_ аргументов

| Model small Vivod macro rg Mov dl, rg Mov ah, 02h Int 21h endm .data .. .code .. vivod al .. | Model small sravnenie macro rg, met cmp rg , ‘a’ ja met add rg, 07h met: add rg, 30h endm .data .. .code .. sravnenie al, m1 .. |

Функционально макроопределения похожи на процедуры. Сходство их в том, что и те, и другие достаточно один раз где-то описать, а затем вызывать их специальным образом. На этом их сходство заканчивается, и начинаются различия, которые в зависимости от целевой установки можно рассматривать и как достоинства и как недостатки:

- в отличие от процедуры, текст которой неизменен, макроопределение в процессе макрогенерации может меняться в соответствии с набором фактических параметров. При этом коррекции могут подвергаться как операнды команд, так и сами команды. Процедуры в этом отношении объекты менее гибки;

- при каждом вызове макрокоманды ее текст в виде макрорасширения вставляется в программу. При вызове процедуры микропроцессор осуществляет передачу управления на начало процедуры, находящейся в некоторой области памяти в одном экземпляре. Код в этом случае получается более компактным, хотя быстродействие несколько снижается за счет необходимости осуществления переходов.

Подключение процедур и макросов во внешнем файле

Внешний файл с расширением inc, а в файле которой использует процедуру или макрос присутствуют следующие строки

Model small

Include [NAME].INC

А вызов макросов и процедур как обычно.

Работа с портами ввода вывода

Адресное пространство памяти в любой микропроцессорной системе семейства х86 делится на пространство адресов памяти и пространство портов ввода/вывода. Это обусловлено архитектурной реализацией и исторической эволюцией процессоров х86.

Для обращения к пространству ввода/вывода используются команды in , out , ins , outs.

In регистр, номер порта – ввод данных из порта в регистр

Out номер порта, регистр – вывод данных из регистра в порт

Ins , Outs - работают с элементами строки памяти.

In ax, 064h ; запись слова в ах из порта 064h

Out 064,al ; запись байта в порт

In ax, dx ; косвенная адресация порта через регистр dx, применяется при использовании 16 разрядного адреса порта

Через порты ввода/вывода осуществляется программирование, контроль и отладка работы периферийных устройств. Зачастую один адрес памяти может служить портом ввода при чтении данных, и портом вывода при записи.

Распределением адресов управляет BIOS через регистры конфигурирования чипсета. Обычно для совместимости аппаратного и программного обеспечения распределение адресов стандартно для любых микропроцессорных систем семейства х86.

ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

Состав любой вычислительной системы одинаков: микропроцессор, электронная память подсистема ввода-вывода. Эти устройство объединяет системная шина, состоящая из следующих шин: данных, адреса и управления.

Каждый микропроцессор имеет определенное число элементов памяти, называемых регистрами, арифметико-логическое устройство и устройство управления. Регистры используются для временного хранения выполняемой команды, адресов памяти, обрабатываемых данных и другой внутренней информации МП. В АЛУ производится арифметическая и логическая обработка данных. Устройство управления реализует временную диаграмму и вырабатывает необходимые управляющие сигналы для внутренней работы МП и связи его с другой аппаратурой через внешние шины МП.

Структуры различных типов МП могут существенно различаться, однако наиболее важными параметрами являются архитектура, адресное пространство памяти, разрядность шины данных, быстродействие. Архитектуру МП определяет разрядность слова и внутренней шины данных МП. Первые МП основывались на 4-разрядной архитектуре. Первые ПЭВМ использовали МП с 8-разрядной архитектурой, а современные МП основаны на МП с 64- и 32-разрядной архитектурой.

Микропроцессоры используют последовательный принцип выполнения команд, принцип параллельной работы, или конвейерный метод выполнения команд.

Последовательный принцип, при котором очередная операция начинается только после выполнения предыдущей.

Принцип параллельной работы, при которой одновременно с выполнением текущей команды производятся предварительная выборка и хранение последующих команд.

В МП с 32-разрядной архитектурой используется конвейерный метод выполнения команд, при котором несколько внутренних устройств МП работают параллельно, производя одновременно обработку нескольких последовательных команд программы.

Адресное пространство памяти определяется разрядностью адресных регистров и адресной шины МП. Для выборки команд и обмена данными с памятью МП имеют шину данных, разрядность которой, как правило, совпадает с разрядностью внутренней шины данных, определяемой архитектурой МП.

Одним из важных параметров МП является быстродействие, определяемое тактовой частотой его работы, которая обычно задается внешними синхросигналами. Выполнение простейших команд (например, сложение двух операндов из регистров или пересылка операндов в регистрах МП) требует минимально двух периодов тактовых импульсов (для выборки команды и ее выполнения). Более сложные команды требуют для выполнения до 10—20 периодов тактовых импульсов. Если операнды находятся не в регистрах, а в памяти, дополнительное время расходуется на выборки операндов в регистры и записи результата в память.

Скорость работы МП определяется не только тактовой частотой, но и набором его команд, их гибкостью, развитой системой прерываний.

Электронная память

Содержит операнды и программу, которую выполняет МП. Используются два типа электронной памяти: постоянные запоминающие устройства (ПЗУ) и оперативные запоминающие устройства (ОЗУ).

В ПЗУ хранится информация, которую ЭВМ может использовать сразу же после включения питания. Она включает программы инициализации периферийных микросхем, программы ядра ОС и программы обработки прерываний.

Постоянное запоминающее устройство является энергонезависимой памятью: после выключения питания информация в нем сохраняется. Информация в ОЗУ разрушается при выключении питания.

В ОЗУ хранятся оперативные данные и программы, используемые МП. Поэтому микросхемы ОЗУ по быстродействию должны быть согласованы с МП, а емкость ОЗУ (вместе с ПЗУ) должна приближаться к пределу, определяемому адресным пространством МП.

Схемы ввода-вывода

Связь МП с контроллерами ПУ обычно осуществляется через порты ввода-вывода под непосредственным управлением МП или под управлением специализированных контроллеров. Связь МП с ПУ производится через стандартизованные интерфейсы ПУ.

Организация и быстродействие схемы ввода-вывода влияет на быстродействие всей вычислительной системы.

Микропроцессоры

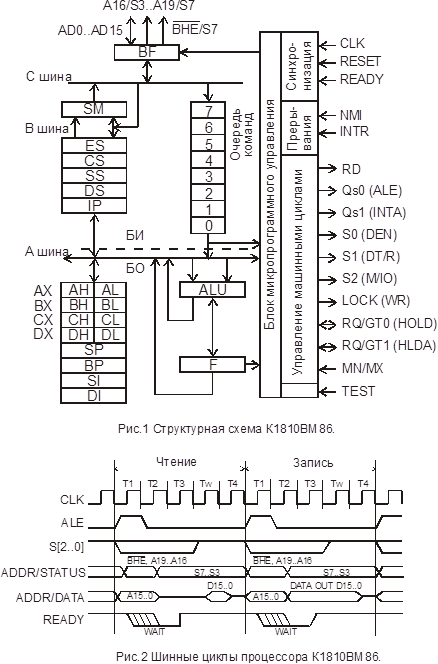

Архитектура однокристального 16-ти разрядного микропроцессора К1810ВМ86.

Аналог I 8086.

Ориентирован на параллельное выполнение выборки и команд, может быть условно разделен на две части, работающие асинхронно: устройство сопряжения с магистралью (БИ – интерфейсный блок) и блок обработки (БО).

Интерфейсный блок обеспечивает формирование 20-разрядного физического адреса памяти, выборку команд и операндов из памяти, организацию очередности команд и запоминание результатов выполнения команд в памяти.

БИ состоит из очереди команд, сегментных регистров, регистра адреса команд, сумматора адреса (SM) и управления машинными циклами.

Устройство сопряжения готово выполнить цикл выборки слова из памяти всякий раз, когда в очереди освобождаются, по меньшей мере, два байта, БО извлекает из нее коды команд по мере необходимости. Очередь организована по принципу «первым пришел — первого обслужили», а шесть ее уровней позволяют удовлетворять запросы БО в кодах команд достаточно эффективно, сокращая тем самым до минимума затраты времени МП на ожидание выборки команд из памяти. Выполнение команд происходит в логической последовательности, предписанной программой, поскольку в очереди находятся те команды, которые хранились в ячейках памяти, непосредственно следующих за текущей командой. При передаче управления в другую ячейку памяти ход выполнения программы нарушается. Устройство сопряжения очищает регистры очереди, выбирает команду по адресу перехода, передает ее УО и начинает новое заполнение этих регистров. При возврате из подпрограммы или из прерывания происходит восстановление очереди команд, адреса которых автоматически вычисляются в СМА. Если МП необходимо выполнить цикл чтения или записи, то выборка команд приостанавливается на время цикла.

Блок обработки предназначен для выполнения операций по обработке данных и состоит из блока микропрограммного управления (БМУ), АЛУ, восьми регистров общего назначения (РОН) и регистра флагов (F).

Команды, выбранные БИ из памяти и записанные в очередь команд, по запросам от БО поступают в БМУ. Это устройство, содержащее память микрокоманд, декодирует команды и вырабатывает последовательность микрокоманд, управляющую процессом обработки. В АЛУ выполняются арифметические и логические операции над 8- и 16-разрядными числами с фиксированной запятой.

Программно-доступными функциональными частями МП являются регистры общего назначения (для хранения операндов и результатов выполнения команд), сегментные (для хранения базовых адресов текущих сегментов памяти), адреса команд и регистр флагов.

Функциональное назначение выводов микропроцессораК1810ВМ86

Вход MN/MX служит для выбора режима функционирования, который предлагает пользователю выбор состава выходных управляющих сигналов в соответствии со степенью сложности проектируемой МП-системы.

В минимальном режиме (вывод MN/MX подключен к шине питания), ориентированном на малые вычислительные системы, МП выдает сигналы управления обменом с памятью и внешними устройствами, а также обеспечивает доступ к системной магистрали по запросу прямого доступа к памяти, используя сигналы HOLD и HLDA. Если вывод MN/MX подключен к шине «Земля» (общий), то МП находится в максимальном режиме и может работать в сложных одно- и многопроцессорных системах. При работе в этом режиме изменяются функции ряда выводов МП.

| Обозначение выводов | Функциональное назначение выводов |

| AD0 .. AD15 | 16-разрядная двунаправленная мультиплексированная шина адреса/данных |

| A16/S3 .. A19/S6 | 4-х разрядная выходная шина микропроцессора, по которой в такте Т1 передаются 4 старших разряда адреса памяти, а в тактах Т2, Т3, Т4, при выполнении операций обращения к памяти и области ввода/вывода – признаки состояния микропроцессора. S4, S3 – указывают номер одного из 4 сегментных регистров, который в данном цикле участвует в формировании исполнительного адреса. S5 – указывает состояние триггера разрешения прерывания S6 – всегда равен 0. |

| BHE/S7 | Выход, 0 на котором в Т1 указывает, что по шине адреса/данных передаются 8-разрядное слово. Сделано для совместимости со старым ПО. В тактах Т2, Т3, Т4 на этом выходе присутствует S7 – признак состояния МП. Если S7=1 – МП находится в состоянии захвата шин внешним устройством. |

| RD | Чтение, выход, 0 на котором означает, что МП осуществляет чтение из памяти или портов ввода/вывода. |

| RЕАDY | Готовность, вход для подачи сигнала окончания цикла работы устройств памяти или ввода/вывода. Используется для синхронизации более медленных памяти или ВУ. |

| INTR | Вход маскируемых запросов на прерывание. Наличие запроса на этом входе анализируется в конце выполнения каждой команды |

| TEST | Вход, проверяемый по команде WFT |

| NMI | Вход немаскируемых запросов на прерывание |

| RESET | Вход начальной установки микропроцессора |

| CLK | Вход для подачи тактовых импульсов |

| MN/MX | Вход для подачи сигнала переключения минимального/максимального режима. |

| Минимальный режим | |

| INTA | Подтверждение прерывания, выходной сигнал стробирующий ввод информации в МП из источника прерывания, вызвавшего переход в режим прерывания |

| ALE | Строб адреса, выходной сигнал, стробирующий в такте Т1 передачу адресной информации с шин МП AD0 .. AD15 на другие элементы системы |

| DEN | Разрешение обмена данными, выходной сигнал, управляющий выдачей информации из шинных формирователей при выполнении команд чтения/записи. |

| DT/R | Ввод/вывод данных, выходной сигнал, указывающий на направление передачи. 1 – МП выдает информацию, 0 – МП принимает данные. |

| M/IO | Память/внешнее устройство, выходной сигнал отличающий передачу данных для памяти или для внешнего устройства. |

| WR | Запись, выходной сигнал указывающий на то, что МП выдает информацию для записи в память/ВУ. |

| HLDA | Разрешение прямого доступа, подтверждение захвата шин МП внешним устройством. |

| HOLD | Запрос прямого доступа (захвата шины) |

| Максимальный режим | |

| QS0, QS1 | Состояние очереди команд |

| S0 .. S2 | Тип цикла обмена, указывает на одну из возможных ситуаций: 000 – признак INTA 001 – ввод информации с ВУ 010 – вывод данных на ВУ 011 – останов 100 – выборка команды 101 – чтение из памяти 110 – запись в память |

| LOСK | Сигнал блокировки, индицирующий, что другое устройство не может занять системную магистраль (запрет на захват системной шины) |

| RQ/GT0, RQ/GT1 | Запрос/разрешение доступа к шине |

Шинные циклы К1810ВМ86

В максимальном режиме, управляющие сигналы системной шины вырабатываются системным контроллером по сигналам состояния процессора. Все сигналы управления (кроме ALE) активны по низкому уровню, что дает возможность раздельно управлять шиной несколькими устройствами.

Для обращения к устройствам ввода/вывода процессор имеет отдельные инструкции IN и OUT, результатом выполнения которых является формирование шинных сигналов IORD и IOWR. В циклах ввода/вывода используют только младшие 16 бит шины адреса, что позволяет адресовать до 64кбайт регистров ввода/вывода. Адрес устройства задается либо в команде, либо берется из регистра DX.

Циклы обращения к портам отличаются от циклов памяти использованием шины адреса. При обращении к портам линии адреса А16..А19 всегда содержат 0, а линии А8..А15 содержат старший байт адреса, только при косвенной адресации через регистр DX. При обращении по непосредственному адресу линии А8..А15 содержат 0.

Цикл подтверждения прерывания аналогичен циклу чтения порта но вместо сигнала IORD, активен сигнал INTA, а состояние шины адреса процессором в это время не управляется.

САМОСТОЯТЕЛЬНО

Дата: 2019-12-22, просмотров: 397.