Рассмотрим логический анализатор, имеющий в своем составе многоразрядное буферное ОЗУ с узлами управления и синхронизации.

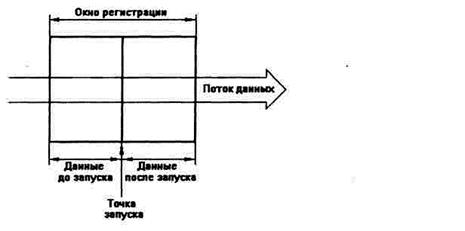

Логический анализатор по своему назначению близок к осциллографу, так как он позволяет наблюдать на экране временные диаграммы сигналов. Но в отличие от обычного (не цифрового) осциллографа логический анализатор работает только с цифровыми двухуровневыми (реже трехуровневыми) сигналами, имеет большое количество входных линий (обычно от 16 до 64), работает в режиме однократного запоминания временных диаграмм (как запоминающий осциллограф) и имеет возможность предпусковой регистрации. Последнее требует некоторых пояснений (рис.1).

В отличие от обычных осциллографов, в которых развертывание формы входного сигнала начинается в момент запуска (то есть прихода внешнего сигнала запуска или превышения входным сигналом заданного уровня напряжения), здесь точка запуска может быть и в начале, и в середине, и в конце окна регистрации. Под запуском здесь понимается временная привязка процесса регистрации к исследуемому процессу. Запуском может служить, например, появление в потоке данных заданного кода или переход (фронт) на одной из входных линий. В этом случае оператор может видеть не только то, что происходило после запуска (как в случае с обычным осциллографом), но и то, что происходило до него.

Логические анализаторы делятся на синхронные (или анализаторы логических состояний) и асинхронные (или анализаторы временных диаграмм). Синхронные анализаторы работают от тактового генератора исследуемой схемы и фиксируют только временные сдвиги, кратные его периоду, а следовательно, выявляют только нарушения в логике работы схемы. Асинхронные анализаторы работают от собственного внутреннего тактового генератора, поэтому они измеряют абсолютные значения временных сдвигов и могут выявлять ошибки из-за неправильно рассчитанных задержек, из-за емкостных эффектов и т.д.

Рис.1. Предпусковая регистрация.

Они обычно делаются гораздо более быстрыми, чем синхронные анализаторы (рассчитываются на предельно возможную частоту регистрации).

Мы в качестве примера будем разрабатывать схему логического анализатора, не отличающуюся рекордными характеристиками ни в плане быстродействия, ни в плане количества разрядов, ни в плане развитости системы запуска. Достоинство ее в другом: она выполняется в виде платы расширения персонального компьютера, и, следовательно, при ее использовании оператор получает в свое распоряжение всю мощь этого компьютера: интеллект, средства ввода и отображения информации, дисковую память и т.д. В результате ценой незначительных дополнительных затрат (цена платы) мы можем превратить компьютер (на время или навсегда) в эффективный и очень удобный логический анализатор.

Исходные данные для проектирования примем следующие: количество входных линий (каналов регистрации) - 32, количество регистрируемых состояний - 4096, максимальная тактовая частота - 10 МГц, тактовый генератор - внутренний с изменяемой частотой или внешний, запуск - по положительному или отрицательному переходу на одной из 8 входных линий, глубина предпусковой регистрации - задается программно.

Первый этап проектирования в соответствии с описанным алгоритмом - предварительная оценка интерфейсной части. Прежде всего посмотрим, какие режимы обмена с магистралью нужны в данном случае. Для обеспечения нужного темпа приема данных (до 10 МГц) совершенно необходимо буферное ОЗУ, обмен с которым должен быть периодическим: при регистрации оно заполняется в темпе тактового генератора, по окончании регистрации его содержимое считывается компьютером. Нужно ли максимально ускорять этот процесс считывания? Зарегистрированная информация должна обрабатываться и отображаться на экране с целью анализа ее оператором. Этот процесс неизмеримо более длительный, чем перекачка информации из буферного ОЗУ в системное ОЗУ компьютера. Поэтому в данном случае особой скорости обмена, по-видимому, не требуется. Конечно же, можно организовать 16-разрядный обмен с нашим УС, дающий большой выигрыш во времени по сравнению с 8-разрядным обменом, но зато он требует дополнительных аппаратурных затрат (вдвое больше буферов данных, формирование сигнала - I/O CS 16). К тому же в этом случае усложняется проектирование печатной платы (нужен второй магистральный разъем). Исходя из всех этих соображений, имеет смысл остановиться на 8-разрядном обмене и отказаться от использования ПДП.

Что касается прерываний, то для логического анализатора их использование очень желательно, если не необходимо. Ведь между началом регистрации и ее окончанием, связанным исключительно с приходом запуска, может пройти довольно большое время. Целесообразно предусмотреть возможность выполнения в этот период компьютером других задач. Поэтому прерывание по окончании регистрации мы будем формировать, что, впрочем, не исключает необходимости чтения флага готовности.

Таким образом, интерфейсная часть нашего одноплатного анализатора должна обеспечивать следующие параметры. Количество адресов УС в адресном пространстве устройств ввода/вывода - 5, из которых четыре используются для чтения зарегистрированных данных, а один - для чтения флага готовности. Для записи управляющего слова будем использовать два из этих пяти адресов (надо записать глубину предпусковой регистрации, код выбора тактовой частоты, код выбора запуска). Используем одно прерывание по окончании регистрации. Как видим, ничего сложного здесь нет, поэтому к интерфейсной части мы не возвращаемся.

Переходим к операционной части. Основные ее узлы: буферное ОЗУ объемом 128 Кбит с организацией 4К х 32, счетчик для перебора адресов, внутренний тактовый генератор с программно изменяемой частотой, схема запуска и входные буфера для регистрируемых сигналов.

ОЗУ целесообразно выполнить на многоразрядных микросхемах (для снижения количества корпусов). Требования к его быстродействию в данном случае невысоки (при максимальной тактовой частоте 10 МГц в течение 100 не необходимо переключить счетчик адресов и записать входную информацию в ОЗУ). Таких микросхем, особенно зарубежного производства, достаточно много.

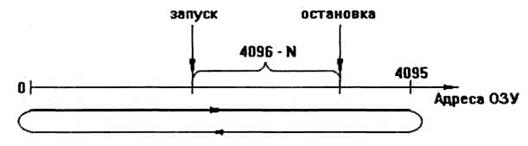

От счетчика требуется максимальное быстродействие (можно взять, например, микросхемы КР531ИЕ17, которые достаточно легко каскадируются без потери быстродействия). Кроме простого перебора адресов счетчик должен также обеспечивать предпусковую регистрацию. Остановимся на этом несколько подробнее. Для того чтобы реализовать предпусковую регистрацию, необходимо до прихода запуска непрерывно переписывать содержимое буферного ОЗУ по кругу (рис.2). Если мы выбираем глубину предпусковой регистрации N тактов, то надо остановить регистрацию через (4096 - N) тактов после прихода запуска. Затем надо считывать содержимое ОЗУ, начиная с точки остановки с перебором адресов в том же направлении, что и при регистрации. Проведя 4096 операций чтения содержимого ОЗУ, мы получим N тактов до запуска и (4096 - N) тактов после запуска, то есть моменту прихода запуска будет соответствовать адрес ОЗУ, считанный N-ым.

Рис.2. Реализация предпусковой регистрации.

Однако все произойдет именно так только в том случае, если от момента начала регистрации до момента прихода запуска наш анализатор успеет зафиксировать N тактов. Иначе мы не перепишем все ОЗУ, и в части его адресов будет находиться предыдущая информация. Чтобы избежать этого, надо запретить реакцию на запуск в течение N тактов после начала регистрации (выдержать своеобразное "мертвое" время). А что будет, если запуск придет в течение этого "мертвого" времени? Если исследуемый процесс периодический, то анализатор среагирует на следующий запуск. Если же процесс однократный, то надо начать процесс регистрации заведомо

раньше (на "мертвое" время или больше), чем начнется изучаемый процесс (например, если мы исследуем старт компьютера при включении питания).

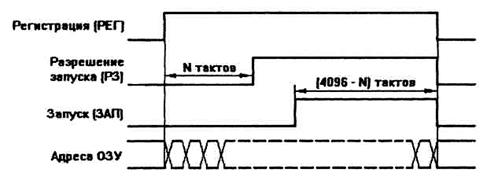

В результате счетчики анализатора должны обеспечивать временную диаграмму, показанную на рис.3. Адреса ОЗУ начинают перебираться с началом регистрации. В течение N тактов после начала регистрации запуск запрещен. Через (4096 - N) тактов после прихода запуска регистрация прекращается.

Рис.3. Временная диаграмма работы счетчиков логического анализатора.

Точно так же может быть реализована предпусковая регистрация в цифровом осциллографе, который, кстати, тоже можно выполнить в виде одноплатного УС, сопрягаемого с системной магистралью. По сравнению с логическим анализатором в схему надо будет добавить одно или несколько АЦП и некоторые другие цифро-аналоговые узлы.

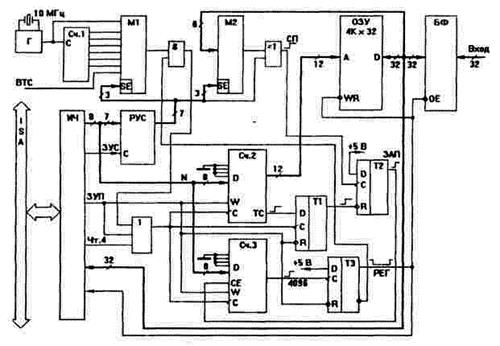

Что касается остальных узлов логического анализатора, то они не представляют особого интереса, поэтому сразу обратимся к функциональной схеме всего УС (рис.4). Здесь мы уже не разрисовываем подробно интерфейсную часть, как мы делали при рассмотрении предыдущего УС, так как ничего принципиально нового она не содержит.

Тактовый генератор выполнен на счетчике Сч.1 и мультиплексоре Ml. Он может выдавать ряд частот, различающихся в 2 раза (период 100, 200, 400, 800, 1600, 3200, 6400 не) или внешний тактовый сигнал ВТС. То есть здесь реализуются как синхронный, так и асинхронный режимы работы. В качестве

запуска используется положительный или отрицательный переход на одной из восьми входных линий, выбираемых мультиплексором М2 (полярность перехода задается управляемым инвертором на элементе "Исключающее ИЛИ").7-разрядное управляющее слово записывается в регистр управляющего слова РУС по сигналу ЗУС (STR W0).

Перед началом работы необходимо записать в наш анализатор управляющее слово и упреждение (глубину предпусковой регистрации).8-разрядный код упреждения N записывается в два 12-разрядных счетчика Сч.2 и Сч. З по сигналу ЗУП (STR W1). При этом на четыре младших входных разряда счетчиков подается сигнал логического нуля (то есть упреждение задается с точностью до четырех тактов и выбирается из ряда: О, 16, 32, 48, 64,..., 4080 тактов).

Запись упреждения служит стартом регистрации (сбрасываются триггера Tl, T2, ТЗ, начинает считать Сч.2, ОЗУ переходит в режим записи, а входной буфер БФ - в режим пропускания). Счетчик Сч.2 работает в режиме вычитания (обратного счета). После того как он отсчитал N тактов, перебрасывается триггер Т1 (заканчивается "мертвое" время).

Рис.4. Функциональная схема логического анализатора.

После этого Т2 начинает реагировать на синхропереход СП. После поступления синхроперехода триггер Т2 перебрасывается и разрешает работу Сч. З, работающего в режиме прямого счета. Затем Сч. З отсчитывает (4096 - N) тактов и перебрасывает ТЗ. На этом регистрация закончена.

Сигнал РЕГ с выхода ТЗ служит флагом готовности и используется для выработки прерывания. По окончании регистрации по четырем адресам компьютер считывает записанную в ОЗУ 32-разрядную информацию. При этом сигнал чтения из четвертого адреса Чт.4 (STR R3) перебрасывает на единицу Сч.2, то есть изменяет адрес ОЗУ. Этот процесс чтения повторяется 4096 раз. В результате полный цикл перекачки зарегистрированной информации включает в себя 16384 обращения к логическому анализатору.

Таким образом, мы рассмотрели проектирование довольно типичного УС с буферным ОЗУ с периодическим режимом обмена. Данный модуль логического анализатора может быть использован в системе динамической отладки УС.

Заключение

Наиболее распространенными устройствами отображения информации являются мониторы на основе ЭЛТ. Принцип действия таких мониторов мало отличается от принципа действия обычного телевизора и заключается в том, что испускаемый электронной пушкой пучок электронов, попадая на экран, покрытый люминофором, вызывает его свечение. Монитор VIEWSONIC 17 GA / GL модели VS1769-GA-1 производства фирмы MATSUSHITA ELECTRIC (PANASONIC) предназначен для работы в стационарных условиях. В нем применена цветная электронно-лучевая трубка с повышенными эксплуатационными характеристиками, в которой использованы электронная пушка с двойной системой излучателей, маска с антистатическим тонирующем покрытием из инвара, а также дополнительная зашита от излучений.

Схема и конструкция монитора VIEWSONIC 17 GA / GL обеспечивают выполнение следующих функций:

обработку и отображение текстовой и графической информации, поступающей в стандартах обмена VGA, SVGA;

поддержку стандарта VESA DDC;

вывод на экран перечня меню;

самотестирование;

оптимизацию задач OSD;

обеспечение высокого качества изображения в широком диапазоне цветовых оттенков;

минимизацию искажений растра;

динамическую фокусировку лучей;

обеспечение цифровой технологии мультиразвертки (8 режимов) с настройкой и отслеживанием заданных параметров;

поддержку микропроцессора системной шины 1%;

хранение в памяти 13 градаций оперативных настроек;

контроль и блокировку смещения (вращения) растра;

высокое качество воспроизведения звука за счет использования встроенных динамических головок;

возможность использования встроенного или внешнего микрофона, а также выносных динамических головок;

подавление помех типа "муар";

адаптацию к колебаниям напряжения питания в диапазонах 90-132 В, 198-264 В.

Наиболее распространенными неисправностями данного монитора являются:

Отсутствует звук

Не работает центровка растра по вертикали

Не работает регулировка размера растра по вертикали

Не работает регулировка размера растра по горизонтали

Отсутствует растр, нет высокого напряжения

Монитор не переключается из дежурного режима в рабочий

При включении питания преобразователь не спускается, предохранитель FS801 не перегорает

При включении питания сгорает предохранитель FS801

На экране отсутствует один из основных цветов, например зеленый

На экране нет отображения служебной информации (OSD). Отсутствует один из основных цветов, например зеленый

Отсутствует растр.

Литература

1. Донченко А.Л. Ремонт зарубежных мониторов. Серия "Ремонт", выпуск 27. М.: СОЛОН-Р. 1999, с. 214.

2. Схемотехника устройств на мощных полевых транзисторах: Справочник. Под. ред. В.П. Дьяконова. М.: Радио и связь. 1994.

3. Дьяконов В., Ремнев А., Смердов В. Особенности ремонта узлов радиоэлектронной аппаратуры на МДП-транзисторах. Ремонт и сервис. 1999, №11. С.58...60.

4. Иванов B.C., Панфилов Д.И. Компоненты силовой электроники фирмы MOTOROLA. M.: ДОДЖА, 1998, с.144.

5. Высоковольтные транзисторы PHILIPS для телевизоров. CHIP news, 1998, № 1. С.39,40.

6. Тук М. Аппаратные средства IBM PC: Энциклопедия.2-е изд. - СПб.: Питер Ком, 2001.

7. ГУК М. Аппаратные средства IBM PC. Энциклопедия. - СПб.: "Питер", 2000. - 816 с: илл.

Дата: 2019-07-30, просмотров: 344.