ПРИЛОЖЕНИЕ 2

Функциональная схема АКА-16 ПРМ

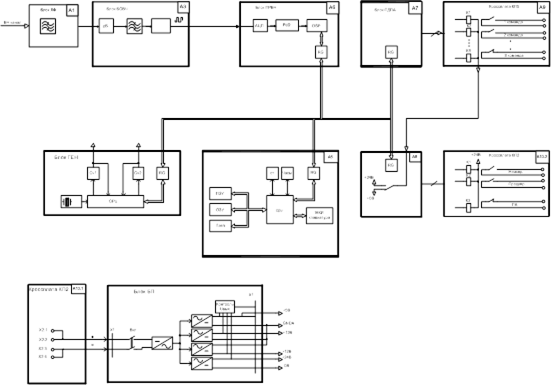

ПРИЛОЖЕНИЕ 3

Функциональная схема управления реле команд

Описание работы функциональной схемы управление реле приема команд

Управление остальными реле построено по аналогичной схеме.

Схема работает следующим образом.

На транзисторе VT1 блока БВ1 построен параметрический стабилизатор напряжения. В исходном состоянии значение напряжения +UK на выходе источника (эмиттер транзистора VT1) равняется 6 В, что недостаточно для срабатывания реле, расположенных на кроссплате КП5. Таким образом, даже при появлении ложной (помеховой) команды на включение реле от блока ПРЦ, реле включено не будет.

Для включения реле выполняются следующие действия.

От блока ПРЦ в блок БВ1 поступает сигнал на включение ключа AV5. Ключ включается и шунтирует параметрический стабилизатор. Напряжение +UK поднимается до +24В. Значение напряжения +UK постоянно контролируется с помощью компаратора DA1, сигнал с которого через оптопару AV4.1 поступает на блок ПРЦ.

От блока ПРЦ на вход оптопары AV1.1 уровнем логического нуля поступает сигнал на включение реле. С выхода оптопары, через один из ключей элемента DD6, сигнал включения, уровнем (0,5-1,0) В поступает на обмотку реле. Реле включается.

Во включенном состоянии, через обмотку реле протекает ток, который открывает соответствующий ключ элемента DD7. Сигнал с выхода ключа, через оптопару AV5.1 поступает в блок ПРЦ для контроля включения реле.

Выключение реле происходит в обратном порядке.

Номинал резистора R1 подобран таким образом, что ключи элемента DD7 открываются даже при пониженном напряжении +UK (6 В). Таким образом, можно в тестовом режиме проверять целостность обмоток реле путем имитации включения реле на пониженном напряжении.

Значение пониженного напряжения +UK (6 В) выбрано исходя из напряжений срабатывания (18 В) и отпускания (12 В) реле.

ПРИЛОЖЕНИЕ 4

/* ADSP-2191 interrupt vector table */

/* locations based upon default interrupt priority at reset. */

/* peripheral mapping to specific interrupts is user-definable. */

/* define external and global variables & labels */

EXTERN start;

//#include "def2191.h"

//.section/pm seg_ivt;

section/pm IVreset;

/* RESET: 0x000 - 0x01F */

JUMP start;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* powerdown: 0x020 - 0x03F */

.section/pm IVpwrdwn;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* loop & PC stack: 0x040 - 0x05F */

.section/pm IVstackint;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* Emulator Kernel/single step: 0x060 - 0x07F */

.section/pm IVkernel;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* Host Port DMA: 0x080 - 0x09F */

//.section/code IVint4;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* SPORT0 Receive: 0x0A0 - 0x0BF */

//.section/code IVint5;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* SPORT0 Transmit: 0x0C0 - 0x0DF */

//.section/code IVint6;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* SPORT1 Receive: 0x0E0 - 0x0FF */

//.section/code IVint7;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

// RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* SPORT1 Transmit: 0x100 - 0x11F */

.section/code IVint8;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* SPORT2 Receive or SPI0: 0x120 - 0x13F */

.section/code IVint9;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* SPORT2 Transmit or SPI1: 0x140 - 0x15F */

.section/code IVint10;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* UART Receive: 0x160 - 0x17F */

.section/code IVint11;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* UART Transmit: 0x180 - 0x19F */

.section/code IVint12;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* Timer A: 0x1A0 - 0x1BF */

.section/code IVint13;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* Timer B: 0x1C0 - 0x1DF */

.section/code IVint14;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/* Timer C, PF Interrupt 0 & 1, Memory DMA: 0x1E0 - 0x1FF */

.section/code IVint15;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI; RTI;

/*row.dsp*/

/*

*******************************************************************

*

* input: sr1 - input sample

* ouput: dm(wns), dm(result), dm(result2);

* shifted: ar, ax0, ax1, ay0, ay1, mx0, mx1, my0, my1, mr

*

*******************************************************************

*/

#include "def2191.h"

#define nsecs 3

#define datalen 2*nsecs+2

#define coeflen 5*nsecs

//nsecs

#define sftcnt 1

#define Buflen 50

#define Hilb_len 102

#define nflt 1

.section/dm seg_dmdata;

.var result[1];

.var result2[1];

.var rowoutput[1], fkoutput[1], n_1;

//.var wns[datalen*nflt];

.var wns[datalen];

.var CurBuffer;

.var Buffer1[Buflen];

.var Buffer2[Buflen];

.var Buffer3[Buflen];

.var Buffer4[Buflen];

.var BufferF1[4*Buflen];

.var BufferOut[16];

.var BufferOutPtr=BufferOut;

.var row_output;

.var Filt2Buf[6];

.var Filt3Buf[6];

.var ptr_Filt2Buf;

.var ptr_Filt3Buf;

.var ptr_FreqPhase;

.var PredResult;

.section/pm seg_pmdata;

/* Config Start Start DMA Next descriptor

word page address count pointer

------ ------ ------ ----- ------

*/

.var _RD_DMA_CONFIG1[5] = 0x8001, 0x0010,Buffer1, Buflen

_RD_DMA_CONFIG2;

.var _WR_DMA_CONFIG1[5] = 0x8003, 0x0000,Buffer1, Buflen,

_WR_DMA_CONFIG2;

.var _RD_DMA_CONFIG2[5] = 0x8001, 0x0010,Buffer2, Buflen,

_RD_DMA_CONFIG3;

.var _WR_DMA_CONFIG2[5] = 0x8003, 0x0000,Buffer2, Buflen,

_WR_DMA_CONFIG3;

.var _RD_DMA_CONFIG3[5] = 0x8001, 0x0010,Buffer3, Buflen,

_RD_DMA_CONFIG4;

.var _WR_DMA_CONFIG3[5] = 0x8003, 0x0000,Buffer3, Buflen,

_WR_DMA_CONFIG4;

.var _RD_DMA_CONFIG4[5] = 0x8001, 0x0010,Buffer4, Buflen,

_RD_DMA_CONFIG1;

.var _WR_DMA_CONFIG4[5] = 0x8003, 0x0000,Buffer4, Buflen,

_WR_DMA_CONFIG1;

.section/pm seg_pmdata;

//.var gain = "dat\gain25.DAT";

//.var coeff[coeflen*nflt]="1140.DAT";

#include "lpf.dsp";

#include "hilbert.dsp"

.section/dm seg_dmdata;

.var lpf[2];

.var n_2;

.var Uinp;

.section/pm seg_pmdata;

//.var Porog[2]={0x03D8,0x7C28};

.VAR coeff1 [coeflen]="Dat\280_el4.dat";

.var Porog1 [5]={0x7f,0xe7,0x17f,0x1e7,0x23f};

.var Porog2 [5]={0x01c,0x02a,0x040,0x070,0xae};

/*.var Coeff2a[11]="Dat\20k_2.dat";

.var Coeff2b[11]="Dat\19_5k_2.dat";

*/.var Coeff2c[10]="dat\17_4k.dat"; //="Dat\19k_2.dat";

/*.var Coeff2d[11]="Dat\18_5k_2.dat";

.var Coeff2e[11]="Dat\18k_2.dat";

.var Coeff3a[6]="Dat\19k_1.dat";

.var Coeff3b[6]="Dat\18k_1.dat";

*/.var Coeff3c[5]="dat\x.dat"; /*="Dat\20k_1.dat";

.var Coeff3d[6]="Dat\18_5k_1.dat";

.var Coeff3e[6]="Dat\19_5k_1.dat";

*/

//.var Fir_flt[1001*2]="Dat\fir.dat";

.section/pm IVint4;

ena sr;

dis int;

mx1=iopg;

mx0 = 0x8001;

mr1 = 0x1;

my0=dmpg1;

dmpg1=0;

//ax0 = 0x1;

/* write the Configuration words for the 2nd transfer, setting the Ownership and DMA enable bits */

iopg = Memory_DMA_Controller_Page;

my1 = 0x8003;

io(DMACW_IRQ) = mr1; /* writing a 1 to this register clears the interrupt */

dm(_RD_DMA_CONFIG1)= mx0;

dm(_WR_DMA_CONFIG1)= my1;

io(DMACW_CPR) = mr1; /* Set the descriptor ready bit in both Write and Read channels */

io(DMACR_CPR) = mr1; /* to signal to the DMA engine that the ownership bit has been set */

dm(_RD_DMA_CONFIG2)= mx0;

dm(_WR_DMA_CONFIG2)= my1;

dm(_RD_DMA_CONFIG3)= mx0;

dm(_WR_DMA_CONFIG3)= my1;

my1 = 0x8007;

dm(_RD_DMA_CONFIG4)= mx0;

dm(_WR_DMA_CONFIG4)= my1;

//io(DMACW_CFG) = mx0;// /* enable DMA in both channels */

//io(DMACR_CFG) = mx0;//

iopg=mx1;

rti(db);

dmpg1=my0;

ena int;

.section/pm seg_pmcode;

.global ini_row,row,Start_DMA;

#define nsecs1 3

.global External_Port_Init;

External_Port_Init:

IOPG = External_Memory_Interface_Page;

ax0=0x38;

// ax1=b#0000000100010010;

ax1=b#0000001011100100;

// ax1=b#0000001111110110;

// || | ++++++---waitstates(2-0 for rd, 5-3 for wr),WaitStateMode (bits 7-6)

// || ++---------00-only ACK, 01 - Only waitStates 10 - both, 11 one of

// |+++-----------ClockDividerSelect bits 10-8: 000=1 : 101=32;

// +--------------WriteHoldEnable if 1 - enables extend the write data hold time by one cycle

IO(EMICTL)=ax0;

ax0=b#0000000001001001;

// ax0=b#0000110111111111;

IO(MS0CTL)=ax1;

IO(MS1CTL)=ax0;//ax1

IO(MS2CTL)=ax0;

IO(IOMSCTL)=ax0;

ax1=0x4001;

IO(MS3CTL)=ax0;

ax0=0xc080;

io(MEMPG10)=ax1;

io(MEMPG32)=ax0;

rts;

Start_DMA:

iopg = Memory_DMA_Controller_Page;

Дата: 2019-07-30, просмотров: 339.