Cодержит два четырехвходовых мультиплексора

4 → 1, которые могут использоваться

и как демультиплексоры.

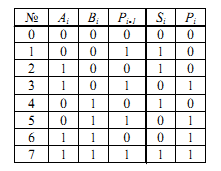

28.Различают полные сумматоры и полусумматоры. Полный сумматор предназначен для сложения трех одноразрядных чисел A, B и C, где в качестве числа C выступает перенос из предыдущего разряда P. В результате выполнения операции сложения в каждом разряде, кроме суммы, может возникнуть перенос в старший разряд P. Для построения схемы сумматора составим таблицу истинности .

Таблица истинности полного сумматора

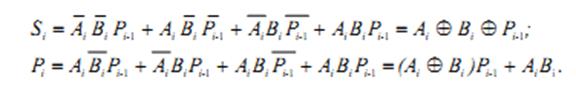

По таблице составим логические выражения СДНФ, описывающие работу полного сумматора:

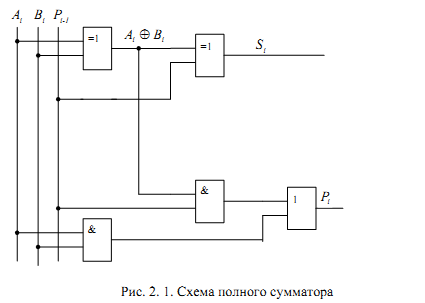

Полученные выражения приводят к достаточно сложной схемной реализации полного сумматора в базисах И-НЕ или ИЛИ-НЕ. Поэтому полный сумматор обычно строится из двух полусумматоров.

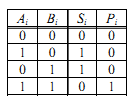

Полусумматор при выполнении операции сложения не учитывает переноса из предыдущего разряда. Работу полусумматора можно описать:

Таблица истинности полусумматора

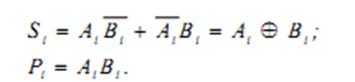

Из таблицы следует:

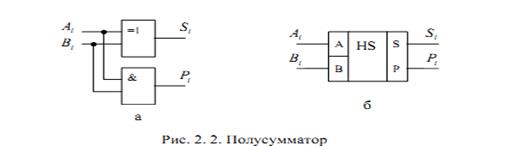

Реализация полусумматора показана на рис. 2.2,а. На рис. 2.2,б показано его условное обозначение.

Полный сумматор строится из двух полусумматоров по схеме приведенной на рис. 2.3,а. Условное обозначение полного сумматора показано на рис. 2. 3,б.

Рис. 2. 3. Схема полного сумматора и его условное обозначение

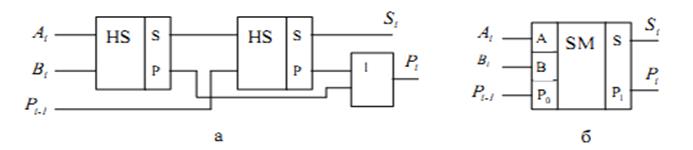

Для сложения n - разрядных чисел требуется один полусумматор в младшем разряде и n- 1 полных сумматоров (рис. 2. 4).

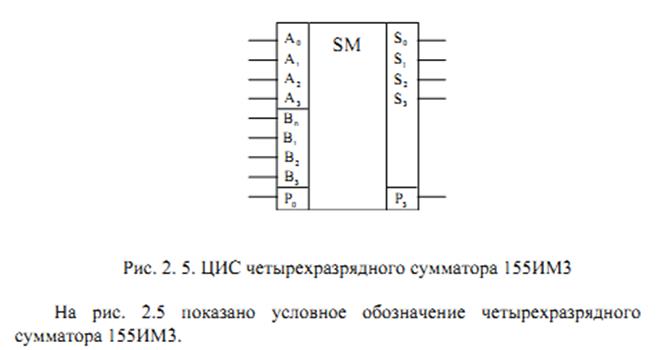

Сумматоры с различной разрядностью выпускаются в виде ЦИС.

Например: 155ИМ1 – одноразрядный сумматор; 155ИМ2 – двухразрядный

сумматор; 155ИМ3 – четырехразрядный сумматор.

29.Триггером называется устройство с двумя устойчивыми состояниями. Триггеры представляют собой простейшие последовательностные устройства и широко используются в электронных устройствах различного назначения как в виде самостоятельных узлов, так и в качестве элементов для построения более сложных цифровых устройств (счетчиков, регистров, запоминающих устройств). К триггерам относят большой класс устройств, отличительной особенностью которых является способность оставаться в одном из двух устойчивых состояний, которые могут изменяться под действием внешних сигналов. При этом состояния триггера распознаются по уровням выходных напряжений, соответствующих уровням “0” и “1”.

Основным свойством триггера является наличие памяти, под которой подразумевается его способность сохранять свое состояние (“0” или “1”) и после прекращения воздействия внешних сигналов. Таким образом, триггер является элементарной ячейкой памяти для хранения одного двоичного разряда числа.

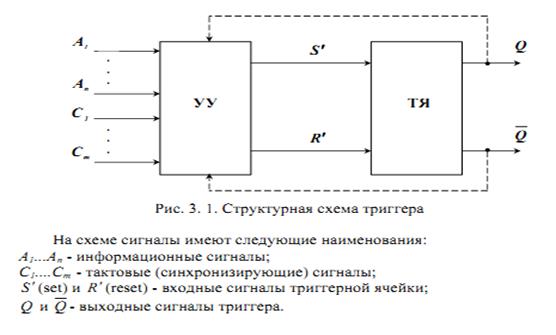

Обобщенная схема триггерного устройства показана на рис. 3.1 и состоит из устройства управления УУ и триггерной ячейки ТЯ.

Существует множество разновидностей триггеров, отличающихся выполняемыми функциями, способами управления записью информации, схемотехническими решениями и т.д. По выполняемым функциям классификацию триггеров производят по состоянию его выходов в момент его срабатывания и после. При этом различают следующие основные виды: RS, JK, T и D - триггеры. По способу управления записью информации различают:

• асинхронные триггеры с записью непосредственно с поступлением информационного сигнала на его вход;

• тактируемые (синхронные) триггеры с записью информации только при подаче тактирующего импульса.

При этом срабатывание триггера может происходить одновременно с поступлением тактирующего импульса (триггер, работающий по уровню), после окончания тактирующего

импульса (триггер с внутренней задержкой), прохождения нескольких тактирующих импульсов (многотактные триггеры), или в моменты изменения состояния тактирующего импульса (синхронизация по фронту).

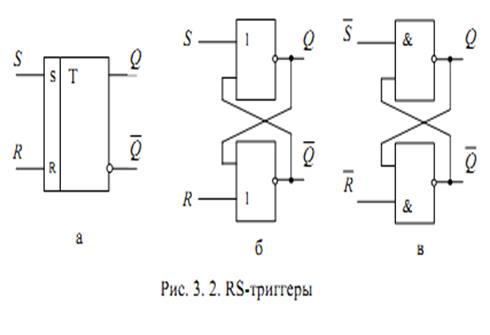

RS – триггеры

RS–триггер имеет два управляющих входа S (set) и R (reset), с помощью которых выполняются установки триггера в то или иное состояние (рис. 3. 2,а):

Q = 1 при S=1 и R=0 ( установка триггера);

Q = 0 при S=0 и R=1 (сброс триггера);

Qn+1=Qnпри S=R=0 (режим хранения предыдущего состояния);

S=R=1 – запрещенная комбинация управляющих сигналов, которая

может привести к неопределенному состоянию триггера.

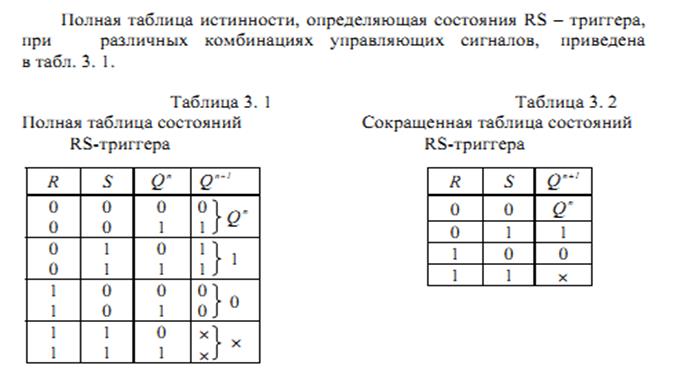

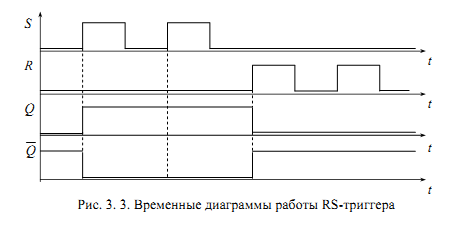

Учитывая связь текущего состояния триггера Qn+1 с предыдущим состоянием Qn при различных комбинациях управляющих сигналов S и R, из табл. 3. 1 можно сформировать сокращенную таблицу истинности (табл. 3. 2). Рассматриваемый триггер является асинхронным, т.к. изменение его состояния происходит непосредственно с поступлением управляющих сигналов. Принцип работы асинхронного RS-триггера поясняется временными диаграммами, показанными на рис. 3. 3.

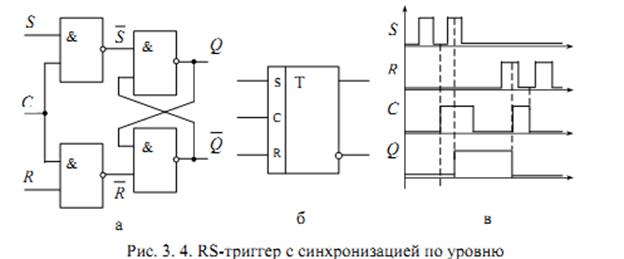

Схемотехнически RS-триггер может быть реализован на элементах 2ИЛИ-НЕ (рис. 3. 2,б) и 2И-НЕ (рис. 3.2,в) с использованием перекрестных положительных обратных связей. В триггере на элементах 2И-НЕ изменение состояния происходит при низких уровнях сигналов S и R . В синхронных RS-триггерах могут быть использованы различные способы синхронизации. На рис. 3. 4,а и б показаны схемотехническая реализация и условное обозначение RS-триггера с синхронизацией по уровню (высокому). На рис. 3. 4,в приведены диаграммы работы такого триггера. Изменение состояний происходит только при высоких уровнях сигнала синхронизации С.

В RS-триггере с синхронизацией по фронту изменение состояния происходит в момент изменения уровня сигнала С. При этом возможна синхронизация как по переднему, так и по заднему фронту (срезу). Такие триггеры строятся по двухступенчатой схеме и в них процессы приема и записи данных разделены во времени. Схема триггера с синхронизацией по заднему фронту и его условное обозначение приведены на рис. 3. 5.

JK-триггеры

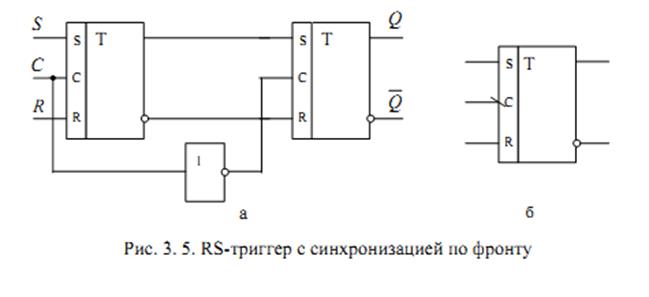

JK-триггер имеет два управляющих входа J (jump) и K (keep) и функционирует подобно RS-триггеру, но при этом не имеет запрещенных комбинаций управляющих сигналов. J - вход подобен S – входу, а K-вход подобен R-входу. При всех комбинациях сигналов на входе, кроме J=K=1, он действует подобно RS-триггеру. При J=K=1 в каждом такте происходит «опрокидывание» триггера и его состояние меняется на противоположное (табл. 3. 3). На рис. 3. 6 показано условное обозначение JK-триггера c синхронизацией по переднему фронту.

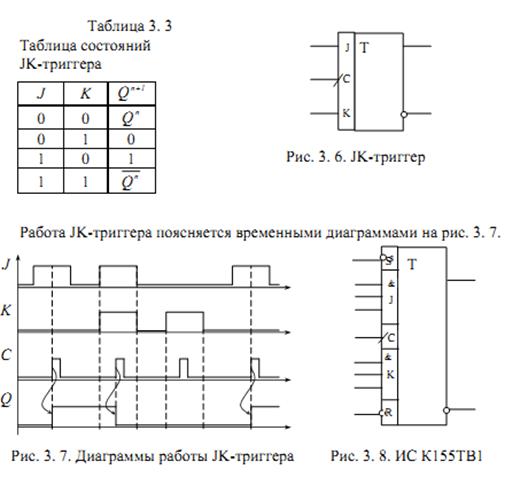

JK-триггеры относятся к универсальным устройствам в отношении их применения как для построения других типов триггеров, так и более сложных устройств последовательного принципа действия. Во всех сериях ИС выпускаются JK-триггеры с различными функциональными возможностями. Например, ИС 155ТВ1 (рис. 3. 8) имеет по три входа J и K, связанных логической операцией И, что существенно расширяет возможности ее применения при реализации различных алгоритмов управления состояниями триггера без применения дополнительных элементов.

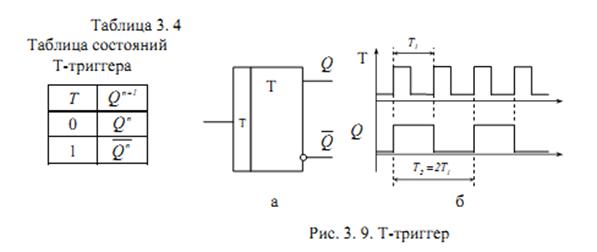

Т-триггеры

Т-триггеры иначе называются счетными и применяются для построения счетчиков и делителей частоты. Такой триггер имеет один тактовый вход и его состояние меняется каждый раз при подаче счетного импульса Т=1 и остается неизменным при Т=0. Таблица состояния триггера приведена в табл. 3. 4. Обозначение Т-триггера и диаграммы работы приведены на рис. 3. 9.

D –триггеры

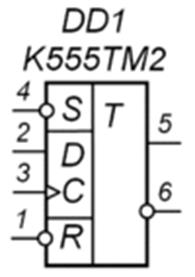

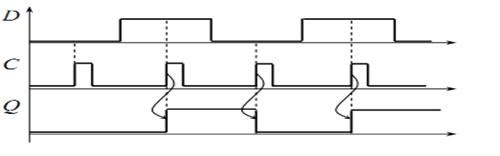

Отличительной особенностью D-триггера (триггера задержки) является то, что он сохраняет информацию, поступившую на D-вход в предыдущем такте работы до прихода синхроимпульса, т.е. его состояние может изменяться с задержкой на один такт. Синхронизация работы производится по переднему или заднему фронту. Условное обозначение D-триггера с синхронизацией по переднему фронту и диаграммы его работы показаны на рис. 3. 11.

Дата: 2019-07-24, просмотров: 523.