Первые процессоры, появившиеся в персональных ЭВМ были 16-разрядные. Процессор, стоявший в компьютере IBM PC, был изготовлен фирмой Intel, назывался i8086 и работал на тактовой частоте 4,77 МГц. Процессоры следующего поколения, 80186, 80188, 80286, тоже были 16-ти разрядными, хотя имели более высокую тактовую частоту и возможность работы с памятью выше 1 Мбайта в защищенном режиме .

Коротко 16-ти битные процессоры можно описать:

· Разрядность ядра - 16 бит

· Число регистров - 14

· Разрядность шины данных : внутренняя - 16 или 8 бит, внешняя - 16 бит

· Адресная шина - 20 бит (память до 1 Мбайта)

· Внутренняя кэш-память - отсутствует

· Внешняя шина для подключения устройств ввода/вывода - ISA (Industry Standard Architecture), 16 бит, 8 МГц

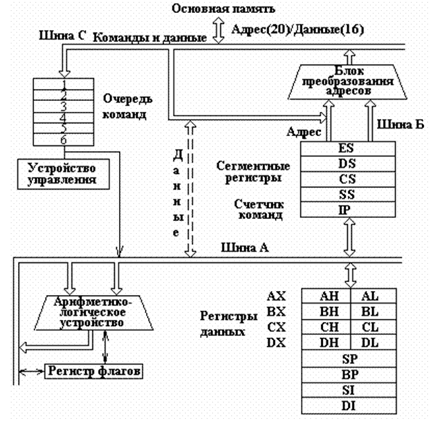

На рисунке представлена структурная схема микропроцессора 8086, в состав которого входят: устройство управления, арифметико-логическое устройство, блок преобразования адресов и регистры.

Устройство управления дешифрирует коды команд и формирует необходимые управляющие сигналы.

Арифметико-логическое устройство осуществляет необходимые арифметические и логические преобразования данных. Выполнение арифметических операций фиксируется флагом:

CF – признак переноса из старшего разряда при выполнении операции

ZF – признак нуля: 1 - число = 0

AF – признак дополнительного переноса, сигнал, возникающий между тетрадами в двоичной операции.

SF – признак знака: 1 - число < 0, 0 - число > 0

PF – признак четности;

ОF – признак переполнения;

DF – признак направления;

IF – признак прерывания;

ТF – признак трассировки;

В блоке преобразования адресов формируются физические адреса данных, расположенных в основной памяти. Наконец, регистры используются для хранения управляющей информации: адресов и данных.

Всего в состав микропроцессора i8086 входит четырнадцать 16-битовых регистров (см. рис.):

a) четыре регистра общего назначения (регистры данных):

AX - регистр-аккумулятор,

BX - базовый регистр,

СХ - счетчик,

DX - регистр-расширитель аккумулятора (по умолчанию для хранения данных в командах умножения и деления);

б) три адресных регистра:

SI - регистр индекса источника,

DI - регистр индекса результата,

BP - регистр-указатель базы (позволяет прочитать произвольный элемент стека);

в) три управляющих регистра:

SP - регистр-указатель стека (адрес последнего числа, записанного в стек),

IP - регистр-счетчик команд (указывает адрес команды, подлежащей выполнению, т.е. следующей),

регистр флагов;

Данные регистры составляют сверхоперативную память.

г) четыре сегментных регистра:

CS - регистр сегмента кодов,

DS - регистр сегмента данных,

ES - регистр дополнительного сегмента данных,

SS - регистр сегмента стека.

Способы адресации

Процессор при обработке программы взаимодействует с оперативной памятью, которая представляется единым массивом однобайтных ячеек, обращение к которым происходит по их номерам (физическим адресам). Число ячеек зависит от разрядности шины адреса и составляет для процессора i8086 1Мбайт.

Для обращения к памяти процессор предварительно помещает адрес ячейки в один из своих регистров. Шестнадцатиразрядный процессор i8086 не может хранить в своих регистрах двадцатиразрядный адрес, поэтому в нем применена так называемая сегментация памяти, которая заключается в том, что истинный, физический адрес ячейки хранится в двух регистрах. Один из них – сегментный (хранит адрес начала блока памяти). Второй регистр хранит величину смещения адреса требуемой ячейки от начала сегмента. Адрес ячейки памяти записывается в виде двойного слова (4 байта): <сегмент>:<смещение>.

Команды могут формировать адреса операндов различными способами. Реализованы следующие режимы адресации:

1. Регистровая прямая (посылочная) - операнд находится в регистре.

Обозначение - <регистр>,< регистр > - АХ, ВХ, СХ, DX, SI, DI, BP, SP, AL, BL, СL, DL, AH, BH, CH, DH.

Пример: (приведен операторами языка ассемблера)

mov АХ,SI ; переслать содержимое регистра SI в регистр АХ.

2. Непосредственная - непосредственный операнд (константа) присутствует в команде.

Обозначение - < константное выражение > .

Пример:

mov AX, 093Ah ; занести константу 093Ah в регистр АХ.

3. Прямая (абсолютная)- исполнительный адрес операнда присутствует в команде.

Обозначение - < переменная >+/-< константное выражение >.

Пример:

mov AX, WW ; переслать в АХ слово памяти с именем WW

mov BX, WW+2 ; переслать в ВХ слово памяти отстоящее от переменной с именем WW на 2 байта.

4. Регистровая косвенная - регистр содержит адрес операнда.

Обозначение - [< регистр >], < регистр > - ВХ. ВР. SI, DI.

Пример:

mov [ BX ], CL ; переслать содержимое регистра CL по адресу, находящемуся в регистре ВХ.

5. Регистровая относительная - адрес операнда вычисляется как сумма содержимого регистра и смещения.

Обозначение - < переменная >[< регистр >] или [< регистр >]< константное выражение >, < регистр > - SI или DI индексная адресация, ВХ или ВР - базовая адресация.

Пример:

mov АХ, WW[SI] ; переслать в АХ слово из памяти, адрес которого вычисляется как сумма содержимого регистра SI и смещения WW.

6. Индексно - базовая - адрес операнда вычисляется как сумма содержимых базового и индексного регистров и смещения.

Обозначение - [< базов. регистр>][< индексн. регистр>] или <переменная >[<базов. регистр >][< индекс. регистр >] или [<базов. регистр >][< ин-декс. регистр >]< константное выражение>, где < индекс. регистр > - SI или DI, < базов. Регистр > - ВХ или ВР.

Пример:

mov [BX+ SI+ 2], CL; переслать содержимое регистра CL по адресу, вычисляемому как сумма содержимого регистров ВХ, SI и константы 2.

7.Стековая адресация - реализует неявное задание адреса операнда. Хотя адрес обращения в стек отсутствует в команде, он формируется с помощью указателя SP в котором автоматически при записи или чтении устанавливается номер последней занятой ячейки стека.

Прерывания

Прерывания осуществляют механизм переключения с одной задачи на другую. Прерывания рассматриваются с двух сторон:

- программно определенные события (предусмотрены текущей программой),

- события не предопределенные, поэтому процессор должен переключаться на какую-то задачу

Следовательно, различают 2 вида прерываний: аппаратные и программные.

1. Программные вызываются из программы с помощью команды int.

2. При аппаратном прерывании процедура прерывания инициируется внешним сигналом IRQ, поступившим с программируемого контроллера прерываний (КПР). Обработка запроса в КПР происходит по следующей схеме:

Происходит фиксация запросов и их селекция по принципу приоритета, который задается номером: запрос с меньшим номером имеет высший приоритет, и наоборот.

КПР выдает сигнал int в процессор. Периодически в конце каждой команды процессор анализирует сигнал int. Если это событие произошло, то процессор прекращает выполнять текущую операцию и приступает к процедуре прерывания:

ЦП записывает в стек содержимое регистра флагов IF (флаг разрешения прерывания), CS и указатель IP, чтобы сохранить состояние текущей команды в момент прерывания. Затем он сбрасывает флаг и передает управление программе обработки прерывания, загружая в регистр CS и IP адрес вектора прерываний, который представляет собой 2 числа (4 байта), задающие местонахождение обработчика прерывания. В оперативной памяти размещаются 256 векторов прерываний (1024 байта).

Адрес вектора прерывания с номером прерывания N вычисляется как N*4. В младшем байте хранится значение IP, а в старшем CS.

Чтобы вернуться из прерывания, необходимо использовать команду iret, которая восстанавливает из стека содержимое CS, IP и регистра флагов.

Программные прерывания применяются в первую очередь для вызова системных обслуживающих программ - функций DOS и BIOS. Большая часть векторов прерываний зарезервирована для выполнения определенных действий; часть из них автоматически заполняется адресами системных программ при загрузке системы. Вектора прерываний можно условно разбить на следующие группы:

векторы внутренних прерываний процессора (0lh, 02h и др.);

векторы аппаратных прерываний (08h...0Fh и 70h...77h);

программы BIOS обслуживания аппаратуры компьютера (10h, 13h, 16h и др.);

программы DOS (21h, 22h, 23h и др.);

адреса системных таблиц BIOS

Запоминающие устройства ЭВМ

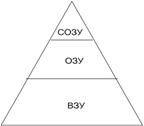

Ключевым принципом построения памяти ЭВМ является ее иерархическая организация (принцип, сформулированный еще Джоном фон Нейманом), которая предполагает использование в системе памяти компьютера запоминающих устройств (ЗУ) с различными характеристиками.

ВЗУ – энергонезависимая память, используемая для хранения больших объемов информации. Её емкость больше, чем в ОЗУ, но быстродействие во много раз меньше.

ОЗУ используется для хранения данных и программ (RAM – устройство с произвольным доступом). ОЗУ характеризуется следующими параметрами:

1. Время обращения: время чтения, время записи.

2. Емкость – количество адресуемых элементов в памяти. Ячейка памяти – то, что считывается за одно обращение. Количество данных (разрядность), считываемых за одно обращение называется шириной выборки. Адресуемый элемент <> ширины. Емкость может рассматриваться как физическая и как размер адресного пространства.

2. Емкость – количество адресуемых элементов в памяти. Ячейка памяти – то, что считывается за одно обращение. Количество данных (разрядность), считываемых за одно обращение называется шириной выборки. Адресуемый элемент <> ширины. Емкость может рассматриваться как физическая и как размер адресного пространства.

Все современные ОЗУ – полупроводниковые устройства:

1. Статические ОЗУ.

В качестве элемента памяти используется триггер. Статические ЗУ обладают меньшей плотностью хранения информации. Однако триггер со времен первых компьютеров был и остается самым быстродействующим элементом памяти. Поэтому статическая память позволяет достичь наибольшего быстродействия, обеспечивая время доступа в единицы и даже десятые доли наносекунд, что и обусловливает ее использование в ЭВМ, главным образом, в высших ступенях памяти – кэш-памяти всех уровней. Триггер создается на двух транзисторах, охваченных обратной связью, и имеет два различных устойчивых состояния. Статические ОЗУ поддерживают режимы хранения, чтения, записи, чтения и записи. Главными недостатками статической памяти являются ее относительно высокие стоимость и энергопотребление.

2. Динамические ОЗУ.

Запоминающая ячейка представляет собой один моп-транзистор, который управляется напряжением и ведет себя практически как ключ. Недостатки, связанные с необходимостью регенерации информации из-за утечки тока и относительно невысоким быстродействием, компенсируются другими показателями малыми размерами элементов памяти и, следовательно, большим объемом микросхем этих ЗУ, а также низкой их стоимостью.

СОЗУ – сверхоперативное запоминающее устройство. Его быстродействие примерно в 100 раз больше быстродействия ОЗУ (реализовано на той же базе, что ЦП, поэтому по быстродействию сравнимо с ним), но емкость в несколько раз меньше.

1. Регистровая СОЗУ.

Входит в состав процессора и представляет собой набор регистров процессора, которые являются линейками триггеров. Предназначена для хранения небольшого количества информации (до нескольких десятков слов, а в RISC-архитектурах – до сотни), которая обрабатывается в текущий момент времени или часто используется процессором. Это позволяет сократить время выполнения программы за счет использования команд типа регистр-регистр и уменьшить частоту обменов информацией с более медленными ЗУ ЭВМ. Реализует возможность одновременных чтения и записи данных. Недостатком является очень быстрое заполнение по мере выполнения задач.

2. Кэш-память (буферная).

Её назначение состоит в сокращении времени передачи информации между процессором и более медленными уровнями памяти компьютера. Обеспечивает автоматическую подмену наиболее часто используемых данных кэш-ячейками, т.е. временно ячейка КЭШа заменяет собой ячейку оперативной памяти. Классический кэш представляет собой ассоциативное ЗУ, т.е. информация ищется по некоторому признаку. Кэш эффективен, когда ЦП долго работает с локальной областью памяти, в противном случае возникают коллизии.

Кэш обычно дублирует группу соседних ячеек памяти (блок) для улучшения временных характеристик.

Около 90% всех обращений удовлетворяется КЭШем.

Кэш прямого отображения строится на базе статических ОЗУ.

За каждой ячейкой памяти зафиксирован свой уровень, на котором она продублирована, поэтому при поиске осуществляется одно сравнение. Но в случае, когда у нескольких ячеек один уровень, эффективность КЭШа снижается.

По степени близости к ЦП различают:

L1 – кэш первого уровня (внутренний) – встроен в ЦП, раздельный (один – для хранения команд, два – данных);

L2 - либо также входит в микросхему процессора, либо может быть реализован в виде отдельной памяти, непосредственно подключенной к ЦП;

L3 (используется редко) – в виде отдельного устройства, которое крепится к той же шине, что и память.

Как правило, на параметры быстродействия процессора большее влияние оказывают характеристики кэш-памяти первого уровня.

Время обращения к кэш-памяти, которая обычно работает на частоте процессора, составляет от десятых долей до единиц наносекунд, т.е. не превышает длительности одного цикла процессора.

Интерфейсы

Под интерфейсами понимаются:

- шины (связывающие устройства),

- процедуры обмена информацией по этим шинам,

- механические подключения (разъёмы).

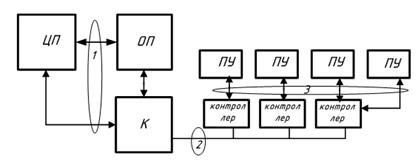

ПУ – периферийные устройства

К – канал ввода/вывода (в/в)

В вычислительной системе различают:

1) интерфейс «процессор - оперативная память – процессор – каналы ввода/вывода» (самый быстрый);

2) интерфейс ввода/вывода (расширения), с помощью которого контроллеры ПУ подключаются к системе;

3) интерфейс периферийных устройств, с помощью которого они подключаются к своим контроллерам (адаптерам). Адаптер – простейшее устройство, преобразующее сигналы одного интерфейса в сигналы другого. Контроллер – более сложная система (блок управления).

Виды интерфейсов

По способу передачи

1. Параллельные: разряды данных передаются одновременно, параллельно (шины ISA, PCI, IDE, Centronics).

2. Последовательные: информация передается последовательно по одному биту (шины USB, RS-232)

Синхронизация обмена

2 способа синхронизации:

1) механизм стробирования данных: по линии шины данных передаются либо “1” либо “0” Для того чтобы приемник надежно различал эти события, используют специальный стробирующий сигнал, который подается одновременно с данными в момент времени, когда на линии устанавливаются действительное значение данных.

2) синхронизация квитированием. Данный способ использует для реализации 2 сигнала – прямой и обратный. После того, как данные с передающего устройства будут зафиксированы в принимающем устройстве, последнее выдаст сигнал, что данные приняты, затем будет выдан сигнал о готовности принимать следующую информацию.

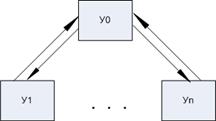

По топологии (характеру связи между устройствами) бывают:

1) с индивидуальной (радиальной) системой шин, которая включает в себя

- главное устройство, к которому подключаются другие, ведомые;

-провода прямой и обратной передачи;

- сигналы синхронизации и управления (сигнал выборки со стороны главного устройства, указывающий, что с главным устройством устройству можно работать).

У - устройство

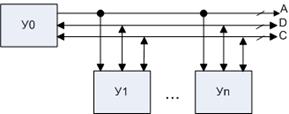

2) с коммунальной (магистральной) системой шин: все устройства взаимодействуют через общую магистраль.

У0 выставляет по шине адреса номер вызываемого абонента. Каждое устройство сравнивает его со своим. В случае совпадения устройство начинает работать (только одно) В противном случае, устройство не реагирует на сигнал.

А – шина адреса

D – шина данных

С – шина управления и синхронизации

Организация ввода/вывода

Организацией обмена между системой и периферийными устройствами управляет комплекс аппаратно-программных средств, называемый каналом ввода/вывода.

2 типа:

- программно управляемые (ПУК)

- канал прямого доступа в память (КПДП)

1. В программно-управляемых каналах при обмене информацией используется аппаратура ЦП с помощью команд IN/OUT (обмен между регистрами и портами ввода/вывода)

Скорость обмена определяется самым медленным устройством.

По производительности устройства делятся на классы:

Низкоскоростные: передается меньше 1000 символов/сек (например, клавиатура,)

Среднескоростные: до 100000 символов/сек (принтер, дискеты)

Высокоскоростные: более 100000 символов/сек (видеокарта, диски).

ЦП видит периферийные устройства как порты. Каждое устройство логически представлено в виде нескольких портов:

- порты (регистры) данных на в/в;

- регистр управления, содержимое которого формируется ЦП-ом и передается в периферийное устройство, его разряды используются для задания операций

- регистр состояния (статусный): отдельные биты формируются периферийным устройством и передаются в ЦП (7-ой и 15-ый бит указывают на готовность участия в обмене: «готов/не готов», «ошибка/нет ошибки»).

При программной реализации алгоритма обмена, в свою очередь, различают два способа в/в, в зависимости от того, каким образом обнаруживается готовность ПУ к обмену:

1. Путем опроса флага готовности ПУ

2. По прерываниям процессора от ПУ.

Алгоритм обмена, основанный на опросе флага готовности (ввод- вывод по условию готовности) включает следующие шаги.

1. На этапе начальной подготовки ЦП опрашивает состояние ПУ (включено, исправно, свободно) и запускает механизм ПУ.

Функционирование ПУ начинается лишь после того, как носитель информации достигнет рабочей скорости. Только после этого начинается обмен информацией с носителем, то есть этап передачи данных.

2. Контроллер ПУ обеспечивает управление процессом считывания (записи) информации с носителя. Считывание (запись) информации обычно осуществляется байтами данных. Прочитанный с носителя байт заносится в буферный регистр данных (РД), после чего устанавливается флаг ГТ (Готов). В случае записи контроллер ПУ обеспечивает перепись байта данных из регистра данных на носитель, после чего устанавливается флаг ГТ, что означает готовность принять из ЭВМ очередной байт данных.

Процессор, обнаружив факт установки флага, осуществляет ввод (вывод) данных из РД, а контроллер ПУ - сброс флага ГТ. Далее процессор формирует адрес ячейки памяти, с которой ведется обмен и подсчитывает количество переданной информации.

Далее осуществляется анализ на конец передачи блока данных и, если переданы еще не все данные, то выполняется сканирование флага готовности.

3. На этапе завершения обмена опрашивается состояние ПУ и выключается механизм ПУ, приводящий в движение носитель информации.

Рассмотренный способ обмена обладает существенным недостатком - непроизводительные затраты процессорного времени на ожидание готовности ПУ.

В/в по прерываниям процессора с точки зрения производительности ЭВМ более эффективен, так как время ожидания готовности ПУ процессор может использовать для выполнения другой программы. При этом способе в момент готовности контроллер ПУ вырабатывает сигнал прерывания, по которому процессор прерывает выполнение текущей программы и приступает к обслуживанию данного ПУ. Обслуживание осуществляется путем передачи управления специальной подпрограмме обмена, написанной для данного ПУ, которая обеспечивает обмен с РД ПУ. После ее завершения управление возвращается прерванной программе. Сигналов прерывания вырабатывается столько, сколько байтов информации вводится (выводится). Недостаток обмена по прерываниям процессора - это ощутимые накладные расходы времени на передачу одного байта данных, поэтому обмен по прерываниям процессора применяется для обслуживания медленнодействующих ПУ (клавиатура, принтер и т. п.).

2. Контроллер прямого доступа в память (КПДП).

Обменом управляет специальный контроллер или сопроцессор ввода/вывода , который инициализируется ЦП и передает данные от заданного ПУ в заданную область ОП, или наоборот.

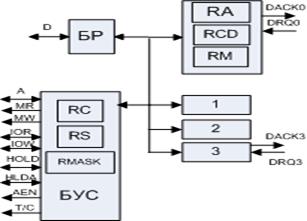

DRQ – запрос на обмен, который говорит, что устройство готово участвовать в обмене

DASK – разрешение запроса

БР – буферный регистр

БУС – блок управления синхронизации

КПДП состоит из 4 одинаковых каналов. Каждый канал содержит 3 регистра: управляющие процедурой обмена с данным устройством:

RA – регистр адреса области памяти, участвующей в обмене (16-разрядный),

RCD – счетчик данных (количество байт, участвующих в операции (макс. 64 Кбайт))

RM – регистр режима, который задает направление обмена между ОП и ПУ.

Канал может работать в 4 режимах:

1) побайтный обмен: передав 1 байт, КПДП отключается и дает возможность работать ЦП или другим устройствам;

2) блочный обмен: начавшаяся операция будет поддерживаться, пока не передадутся все данные.

в) блочный обмен с ожиданием: контроллер будет выполнять операцию, не пуская другие устройства к работе

г) режим каскадного подключения.

3 фазы работы КПДП.

1. Инициирование.

2. Обмен.

3. Завершение.

В канал загружается адрес, количество слов, режим работы канала. Соответствующий канал размаскировывается, ЦП переключается на другую работу. ПУ, когда готово участвовать в обмене, передает сигнал DRQ, который анализируется контроллером. Контроллер посылает в ЦП сигнал HOLD (уступить шину). ЦП отключается от системной шины и передает контроллеру сигнал HLDA (освободил). Контроллер устанавливает сигнал AEN, вследствие чего все устройства отключаются от системной шины, кроме пославшего сигнал.

После этого контроллер выдает ПУ сигнал DACK. Этот сигнал после завершения обмена убирается, счетчик данных уменьшается на 1, контроллер убирает HOLD и AEN, ЦП захватывает шину и убирает HLDA. Контроллер готов реагировать на следующий сигнал DRQ.

Дата: 2019-07-24, просмотров: 392.