Описание счетчика Add:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_signed.all;

use IEEE.STD_LOGIC_arith.all;

entity Add is

port (SIn: in std_logic_vector (5 downto 0);

Inc: in std_logic;

Reset: in std_logic;

SOut: out std_logic_vector (5 downto 0));

end Add;

architecture Add of Add is

begin

process (Inc, reset)

begin

if Inc='1' and Inc'event then

SOut<=CONV_STD_LOGIC_VECTOR(((CONV_INTEGER ('0'& SIn))+1), 6);

end if;

if Reset='1'then Sout<= «000000»;

end if;

end process;

end Add;

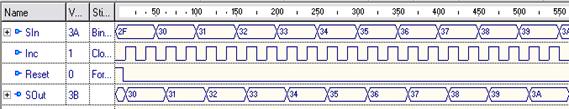

Временная диаграмма работы счетчика Add для УУ:

Описание ALU:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_signed.all;

use IEEE.std_logic_arith.all;

entity ALU is

port (B: in std_logic_vector (7 downto 0);

A: in std_logic_vector (7 downto 0);

SADD: in std_logic;

CLK: in std_logic;

Q: out std_logic_vector (7 downto 0);

FC: out std_logic;

FZ: out std_logic);

end ALU;

architecture ALU of ALU is

signal rez: std_logic_vector (7 downto 0):= «00000000»;

begin

process(CLK)

begin

if CLK='0' and CLK'event then FC<='0';

if SADD='1' then

Q<= CONV_STD_LOGIC_VECTOR((CONV_INTEGER ('0'& A)+CONV_INTEGER ('0'& B)), 9) (7 downto 0) after 4 ns;

FC<= CONV_STD_LOGIC_VECTOR((CONV_INTEGER ('0'& A)+CONV_INTEGER ('0'& B)), 9) (8) after 4 ns;

else Q<= «00000000»;

end if;

if A= «00000000» then FZ<='0';

else FZ<='1';

end if;

end if;

end process;

end ALU;

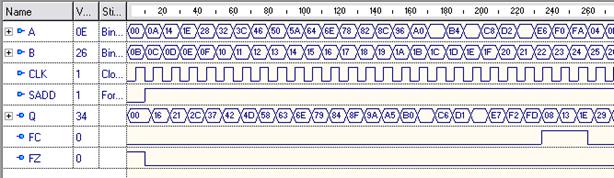

Временная диаграмма работы устройства сложения ALU:

Описание счетчика микрокоманд PC:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_signed.all;

entity PC is

port (RST: in std_logic;

CLK: in std_logic;

PCIn: in std_logic;

IncPC: in std_logic;

AdrIn: in std_logic_vector (7 downto 0);

AdrOut: out std_logic_vector (7 downto 0));

end PC;

architecture PC of PC is

signal reg: std_logic_vector (7 downto 0);

begin

process (CLK, RST)

begin

If CLK='0' and CLK'event and PCIn='1' then reg<=AdrIn;

end if;

If CLK='0' and CLK'event and IncPC='1' then reg<=reg+ «0000001» after 2ns;

end if;

If CLK='1' and CLK'event then AdrOut<=reg after 2ns;

end if;

if RST='1' then reg<= «00000000»;

end if;

end process;

end PC;

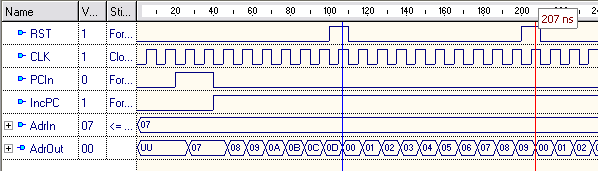

Временная диаграмма работы счетчика микрокоманд PC:

Описание регистров РОН и их выбора:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity R0 is

port (RST: in std_logic;

CLK: in std_logic;

C: in std_logic;

RIn: in std_logic;

ROut: in std_logic;

DataIn: in std_logic_vector (7 downto 0);

DataOut: out std_logic_vector (7 downto 0));

end R0;

architecture R0 of R0 is

signal regist: std_logic_vector (7 downto 0);

begin

process (CLK, RST)

begin

if CLK='0' and CLK'event and RIn='1'and C='1' then regist<=DataIN;

end if;

if CLK='0' and CLK'event and ROut='1'and C='1' then DataOut<=regist after 3 ns;

end if;

if CLK='0' and CLK'event and ROut='0' then DataOut<= «ZZZZZZZZ» after 3 ns;

end if;

if RST='1' then regist<= «00000000»;

end if;

end process;

end R0;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity RDC is

port (Number: in std_logic_vector (7 downto 0);

RDCIn: in std_logic;

R1: out std_logic;

R2: out std_logic;

R3: out std_logic;

R4: out std_logic);

end RDC;

architecture RDC of RDC is

begin

process(RDCIn)

begin

if RDCIn='1' and RDCIn'event then

R1<='0';

R2<='0';

R3<='0';

R4<='0';

if Number= «00000001» then R1<='1'after 2ns;

end if;

if Number= «00000010» then R2<='1'after 2ns;

end if;

if Number= «00000011» then R3<='1'after 2ns;

end if;

if Number= «00000100» then R4<='1'after 2ns;

end if;

end if;

end process;

end RDC;

Временная диаграмма работы выбора регистров РОН RDC:

Описание памяти RAM:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_signed.all;

entity RAM is

port (RdWr: in std_logic;

CS: in std_logic;

Adr: in std_logic_vector (7 downto 0);

Data: inout std_logic_vector (7 downto 0));

end RAM;

architecture RAM of RAM is

type MemoryType is array (0 to 8) of std_logic_vector (7 downto 0);

signal Memory: MemoryType:=(

«00000000», – mov A,#d

«00110011», –#d

«00000001», – mov R,#d

«00000001», – number R

«11110110», –#d

«00000010», – add A, Rn

«00000001», – number R

«00000100», – JBC bit, rel

«00000000»); – restart

begin

process (RdWr, CS, Adr)

begin

if RdWr='1' and CS='1' then Data<=Memory (CONV_INTEGER ('0'& Adr)) after 3ns;

end if;

if RdWr='0' and CS='1' then Memory (CONV_INTEGER ('0'& Adr))<=Data;

end if;

end process;

end RAM;

Описание регистра в один бит:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity R_1bit is

port (reg_in, IE: in std_logic;

CLK, Zero:in std_logic;

reg_out: out std_logic);

end R_1bit;

architecture R_1bit of R_1bit is

signal regist: std_logic;

begin

process(CLK)

begin

reg_out<= regist;

if CLK='0' and CLK'event and IE='1' then regist<=reg_in after 2ns;

elsif Zero='1' then regist<='0' after 2ns;

end if;

end process;

end R_1bit;

–

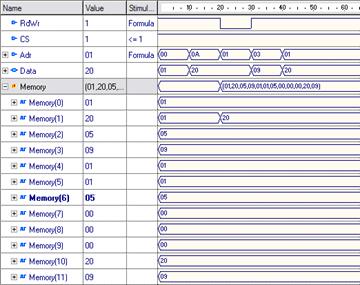

Временная диаграмма работы памяти МПА RAM:

Описание регистра-аккумулятора RA:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity RA is

port (

CLK: in std_logic;

RAIn: in std_logic;

DIn: in std_logic_vector (7 downto 0);

DOut: out std_logic_vector (7 downto 0)

);

end RA;

architecture RA of RA is

signal reg: std_logic_vector (7 downto 0):= «00000000»;

begin

process (CLK, RAIn)

begin

DOut<=reg after 3 ns;

if CLK='0' and CLK'event and RAIn='1' then

reg<=DIn;

end if;

end process;

end RA;

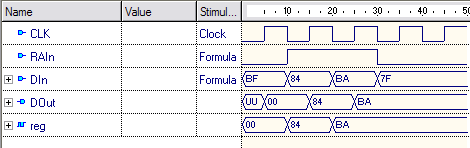

Временная диаграмма работы регистра-аккумулятора RA:

Описание узла памяти Memory:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_signed.all;

entity Memory is

port (Adr: in std_logic_vector (5 downto 0);

RD: in std_logic;

MrOut: out std_logic;

InstrCom: out std_logic_vector (0 to 27));

end Memory;

architecture Memory of Memory is

type MemoryType is array (0 to 59) of std_logic_vector (0 to 27);

signal Memory: MemoryType;

begin

Memory(0)<= «000»& «000000»& «0000000»& «0000000»& «0000»& «0»;

Memory(1)<= «000»& «000000»& «0001000»& «0000000»& «0000»& «0»; – MarIn

Memory(2)<= «000»& «000000»& «0000110»& «0000000»& «0000»& «0»; – RdWr, CS

Memory(3)<= «000»& «000000»& «0000001»& «0000000»& «0000»& «0»; – MbrIn

Memory(4)<= «000»& «000000»& «0000000»& «1000000»& «0000»& «0»; – MbrOut

Memory(5)<= «000»& «000000»& «0010000»& «0000000»& «0000»& «0»; – IrIn

Memory(6)<= «100»& «000000»& «0000000»& «0000000»& «0000»& «0»; – Instr0

– mov A,#d

Memory(7) <= «000»& «000000»& «0100000»& «0000000»& «0000»& «0»; – IncPC

Memory(8) <= «000»& «000000»& «0001000»& «0000000»& «0000»& «0»; – MarIn

Memory(9) <= «000»& «000000»& «0000110»& «0000000»& «0000»& «0»; – RdWr, CS

Memory(10)<= «000»& «000000»& «0000001»& «0000000»& «0000»& «0»; – MbrIn

Memory(11)<= «000»& «000000»& «0000000»& «1000000»& «0000»& «0»; – MbrOut

Memory(12)<= «000»& «000000»& «0000000»& «0000001»& «0000»& «0»; – RAin

Memory(13)<= «001»& «000000»& «0100000»& «0000000»& «0000»& «0»; – Instr2, IncPC

– mov Rn,#d

Memory(14)<= «000»& «000000»& «0100000»& «0000000»& «0000»& «0»; – IncPC

Memory(15)<= «000»& «000000»& «0001000»& «0000000»& «0000»& «0»; – MarIn

Memory(16)<= «000»& «000000»& «0000110»& «0000000»& «0000»& «0»; – RdWr, CS

Memory(17)<= «000»& «000000»& «0000001»& «0000000»& «0000»& «0»; – MbrIn

Memory(18)<= «000»& «000000»& «0000000»& «1000000»& «0000»& «0»; – MbrOut

Memory(19)<= «000»& «000000»& «0000000»& «0000000»& «0010»& «0»; – RDCIn

Memory(20)<= «000»& «000000»& «0100000»& «0000000»& «0000»& «0»; – IncPC

Memory(21)<= «000»& «000000»& «0001000»& «0000000»& «0000»& «0»; – MarIn

Memory(22)<= «000»& «000000»& «0000110»& «0000000»& «0000»& «0»; – RdWr, CS

Memory(23)<= «000»& «000000»& «0000001»& «0000000»& «0000»& «0»; – MbrIn

Memory(24)<= «000»& «000000»& «0000000»& «1000000»& «0000»& «0»; – MbrOut

Memory(25)<= «000»& «000000»& «0000000»& «0000000»& «1000»& «0»; – RIn

Memory(26)<= «001»& «000000»& «0100000»& «0000000»& «0000»& «0»; – Instr2, IncPC

– add A, Rn

Memory(27)<= «000»& «000000»& «0100000»& «0000000»& «0000»& «0»; – IncPC

Memory(28)<= «000»& «000000»& «0001000»& «0000000»& «0000»& «0»; – MarIn

Memory(29)<= «000»& «000000»& «0000110»& «0000000»& «0000»& «0»; – RdWr, CS

Memory(30)<= «000»& «000000»& «0000001»& «0000000»& «0000»& «0»; – MbrIn

Memory(31)<= «000»& «000000»& «0000000»& «1000000»& «0000»& «0»; – MbrOut

Memory(32)<= «000»& «000000»& «0000000»& «0000000»& «0010»& «0»; – RDCIn

Memory(33)<= «000»& «000000»& «0000000»& «0000000»& «0100»& «0»; – ROut

Memory(34)<= «000»& «000000»& «0000000»& «0000000»& «0001»& «0»; – SADD

Memory(35)<= «000»& «000000»& «0000000»& «0001000»& «0000»& «0»; – RZin

Memory(36)<= «000»& «000000»& «0000000»& «0000100»& «0000»& «0»; – RZout

Memory(37)<= «000»& «000000»& «0000000»& «0000001»& «0000»& «0»; – RAin

Memory(38)<= «001»& «000000»& «0100000»& «0000000»& «0000»& «0»; – Instr2, IncPC

– JBC

Memory(51)<= «010»& «110110»& «0000000»& «0000000»& «0000»& «0»; – perexod na adres 36H ili 54 v dec s/s

Memory(52)<= «000»& «000000»& «0000000»& «0000000»& «0000»& «0»; – any value

Memory(53)<= «000»& «000000»& «0000000»& «0000000»& «0000»& «0»; – any value

Memory(54)<= «000»& «000000»& «0100000»& «0000000»& «0000»& «0»; – IncPC

Memory(55)<= «000»& «000000»& «0001000»& «0000000»& «0000»& «0»; – MarIn

Memory(56)<= «000»& «000000»& «0000110»& «0000000»& «0000»& «0»; – RdWr, CS

Memory(57)<= «000»& «000000»& «0000001»& «0000000»& «0000»& «0»; – MbrIn

Memory(58)<= «000»& «000000»& «0000000»& «1000000»& «0000»& «0»; – MbrOut

Memory(59)<= «001»& «000000»& «1000000»& «0000000»& «0000»& «0»; – Instr2, PCIn

process(RD)

begin

if RD='1' and RD'event then

InstrCom<=Memory (CONV_INTEGER ('0'& Adr));

MrOut<='1';

end if;

if RD='0' and RD'event then MrOut<='0';

end if;

end process;

end Memory;

Временная диаграмма работы памяти УУ Memory:

VHDL – описание остальных элементов схемы (регистра CAR и регистра СBR, регистра инструкций, мультиплексора, декодера, простых логических элементов, регистров MAR и MBR):

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity CAR is

port (D: in std_logic_vector (5 downto 0);

CarIn: in std_logic;

CarOut: out std_logic;

Q: out std_logic_vector (5 downto 0));

end CAR;

architecture CAR of CAR is

begin

process(CarIn)

begin

if CarIn='0' and CarIn'event then

Q<=D;

CarOut<='1';

end if;

if CarIn='1' and CarIn'event then CarOut<='0';

end if;

end process;

end CAR;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity CBR is

port (InstrCom: in std_logic_vector (0 to 27);

CbrIn: in std_logic;

Adr: out std_logic_vector (5 downto 0);

Instr0: out std_logic;

Instr1: out std_logic;

Instr2: out std_logic;

PCIn: out std_logic;

IncPC: out std_logic;

IrIn: out std_logic;

MarIn:out std_logic;

RdWr:out std_logic;

CS:out std_logic;

MbrIn:out std_logic;

MbrOut:out std_logic;

MbrInD:out std_logic;

MbrOutD:out std_logic;

RzIn:out std_logic;

RzOut:out std_logic;

Inv:out std_logic;

RAIn:out std_logic;

RIn:out std_logic;

ROut:out std_logic;

RDCIn:out std_logic;

SADD:out std_logic;

InvZ: out std_logic);

end CBR;

architecture CBR of CBR is

begin

process(CbrIN)

begin

if CbrIN='1' and CbrIN'event then

Instr0<=InstrCom(2) after 1ns;

Instr1<=InstrCom(1) after 1ns;

Instr2<=InstrCom(0) after 1ns;

ADR<=InstrCom (3 to 8) after 1ns;

PCIn <=InstrCom(9) after 1ns;

IncPC<=InstrCom(10) after 1ns;

IrIn <=InstrCom(11) after 1ns;

MarIn <=InstrCom(12) after 1ns;

RdWr <=InstrCom(13) after 1ns;

CS <=InstrCom(14) after 1ns;

MbrIn<=InstrCom(15) after 1ns;

MbrOut<=InstrCom(16) after 1ns;

MbrInD<=InstrCom(17) after 1ns;

MbrOutD<=InstrCom(18) after 1ns;

RzIn <=InstrCom(19) after 1ns;

RzOut<=InstrCom(20) after 1ns;

Inv<=InstrCom(21) after 1ns;

RAIn<=InstrCom(22) after 1ns;

RIn <=InstrCom(23) after 1ns;

ROut<=InstrCom(24) after 1ns;

RDCIn <=InstrCom(25) after 1ns;

SADD<=InstrCom(26) after 1ns;

InvZ<=InstrCom(27) after 1ns;

end if;

end process;

end CBR;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity IR is

port (Command: in std_logic_vector (7 downto 0);

IRin: in std_logic;

Reset: in std_logic;

IrOut: out std_logic;

Com: out std_logic_vector (7 downto 0));

end IR;

architecture IR of IR is

begin

process (IrIn, Reset)

begin

if IrIn='1' and Irin'event then

Com<=Command after 2ns;

IrOut<='1'after 2ns;

end if;

if IrIn='0' and Irin'event then IrOut<='0';

end if;

if Reset='1' then

Com<= «00000000»;

IrOut<='1';

end if;

end process;

end IR;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity DC1 is

port (Ale:in std_logic;

Com: in std_logic_vector (7 downto 0);

ComAdr: out std_logic_vector (5 downto 0));

end DC1;

architecture DC1 of DC1 is

begin

process(Ale)

begin

if Ale='1' and Ale'event then

if Com= «00000000» then ComAdr <= «000111»;

elsif Com= «00000001» then ComAdr <= «001110»;

elsif Com= «00000010» then ComAdr <= «011011»;

elsif Com= «00000011» then ComAdr <= «100111»;

elsif Com= «00000100» then ComAdr <= «110011»;

else ComAdr <= «000000»;

end if;

end if;

end process;

end DC1;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity INV is

port (DIn: in std_logic_vector (7 downto 0);

Inv: in std_logic;

DOut: out std_logic_vector (7 downto 0));

end INV;

architecture INV of INV is

begin

DOut<=not DIn when Inv='1'else DIn;

end INV;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity LogAnd is

port (in1: in std_logic;

in2: in std_logic;

Sout: out std_logic);

end LogAnd;

architecture LogAnd of LogAnd is

begin

Sout<=in1 and in2 after 1ns;

end LogAnd;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity LogOR is

port (in1: in std_logic;

in2: in std_logic;

SOut: out std_logic);

end LogOR;

architecture LogOR of LogOR is

begin

SOut<=in1 or in2 after 1ns;

end LogOR;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity MUX is

port (IN1: in std_logic_vector (5 downto 0);

IN2: in std_logic_vector (5 downto 0);

IN3: in std_logic_vector (5 downto 0);

Adr0: in std_logic;

Adr1: in std_logic;

CLK: in std_logic;

MuxOut: out std_logic;

OUT1: out std_logic_vector (5 downto 0));

end MUX;

architecture MUX of MUX is

begin

process(CLK)

begin

if CLK='1' and CLK'event then

if Adr1='0' and Adr0='0' then OUT1 <= IN1;

elsif Adr1='1' then OUT1 <= IN2;

elsif Adr1='0' and Adr0='1' then OUT1 <= IN3;

else Out1<= «000000»;

end if;

MuxOut<='1';

end if;

if CLK='0' and CLK'event then MuxOut<='0';

end if;

end process;

end MUX;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity MAR is

port (RST: in std_logic;

CLK: in std_logic;

MarIn: in std_logic;

AdrIn: in std_logic_vector (7 downto 0);

AdrOut: out std_logic_vector (7 downto 0));

end MAR;

architecture MAR of MAR is

signal reg: std_logic_vector (7 downto 0):= «00000000»;

begin

process (CLK, RST)

begin

if CLK='0' and CLK'event and MarIn='1' then reg<=AdrIn;

end if;

if CLK='1' and CLK'event then AdrOut<=reg;

end if;

if RST='1' then reg<= «00000000»;

end if;

end process;

end MAR;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity MBR is

port (RST: in std_logic;

CLK: in std_logic;

MbrIn: in std_logic;

MbrOut: in std_logic;

MbrInD: in std_logic;

MbrOutD: in std_logic;

DataIn: inout std_logic_vector (7 downto 0);

DataOut: inout std_logic_vector (7 downto 0));

end MBR;

architecture MBR of MBR is

signal reg: std_logic_vector (7 downto 0);

begin

Process (CLK, RST)

begin

if CLK='0' and CLK'event then

if MbrIn='1' then reg<=DataIn;

elsif MbrOut='1' then DataOut<=reg;

elsif MbrInD='1' then reg<=DataOut;

elsif MbrOutD='1' then DataIn<=reg;

end if;

if MbrIn='0' and MbrOutD='0' then DataIn<= «ZZZZZZZZ»;

end if;

if MbrOut='0' and MbrInD='0' then DataOut<= «ZZZZZZZZ»;

end if;

end if;

if RST='1' then reg<= «00000000»;

end if;

end process;

end MBR;

–

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity RZ is

port (DIn: in std_logic_vector (7 downto 0);

CLK: in std_logic;

RST: in std_logic;

RZOut: in std_logic;

RZIn: in std_logic;

InvZ: in std_logic;

DOut: out std_logic_vector (7 downto 0));

end RZ;

architecture RZ of RZ is

signal regist: std_logic_vector (7 downto 0);

begin

process (CLK, RST)

begin

if CLK='0' and CLK'event and RZIn='1' then regist<=DIN;

end if;

if CLK='0' and CLK'event and RZOut='1' then

if InvZ='1'then DOut<=not regist after 3 ns;

else DOut<=regist after 3 ns;

end if;

end if;

if CLK='0' and CLK'event and RZOut='0' then DOut<= «ZZZZZZZZ» after 3 ns;

end if;

if RST='1' then regist<= «00000000»;

end if;

end process;

end RZ;

Дата: 2019-05-29, просмотров: 292.