В состав всех комплектов БИС (в том числе и секционных) входят БИС ОЗУ, ПЗУ, программируемого ПЗУ или ППЗУ, ПЛМ, программируемой ПЛМ или ППЛМ, имеющие разнообразную организацию информационных полей и управляющие интерфейсной логикой. Они позволяют создавать наращиваемые поля оперативной, постоянной и микропрограммной памяти, работать с прямыми и интерфейсными информационными сигналами, строить многовходовые системы адресной выборки, цепи контроля передаваемой и хранимой информации и т.д.

Логическая структура процессора на основе комплекта БИС секционного микропроцессора

Развитая внутренняя структура секционных комплектов БИС микропроцессора обеспечивает возможность построения высокопроизводительных средств эффективной эмуляции развитых микро-ЭВМ и позволяет создавать гибкие эффективные системы с адаптацией к области применения.

Развитая внутренняя структура секционных комплектов БИС микропроцессора обеспечивает возможность построения высокопроизводительных средств эффективной эмуляции развитых микро-ЭВМ и позволяет создавать гибкие эффективные системы с адаптацией к области применения.

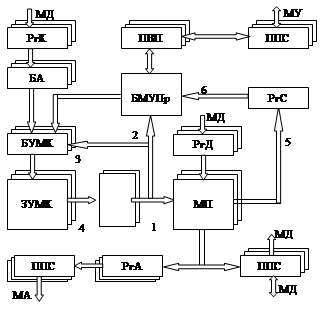

Рис.10 Обобщенная структрура процессора на основе БИС комплекта секционного микропроцессора

Обобщенная структура процессора на основе комплекта БИС приведена на рис.10. В основу процессора положены секции микропроцессоров МП и секции ускоренного опережающего переноса (Рассматриваемые микропроцессоры могут быть построены на основе микропроцессорных комплектов серий КР582, К583, КР584, К589, К1800, КР1802, КР1804, U83-К1883). Для построения интерфейсных схем применены секции приемопередатчиков сигналов ППС, позволяющие организовать двунаправленные магистрали данных, адресов и сигналов управления. Блок микропрограммного управления строится на основе ПЗУ или ППЗУ, а также БИС выработки последовательности управляющих сигналов. Последние применяются в качестве блока управления микрокомандами БУМК. Для управления приоритетными векторными прерываниями используются соответствующие секции БИС ПВП для построения регистров – секции БИС регистров универсального назначения. Блок местного управления БМУ управляет всей системой.

Поскольку секции микропроцессора имеют некоторый набор рабочих регистров общего назначения, любые из них могут быть выделены в качестве счетчика команд, регистра – указателя стека или других рабочих и управляющих регистров.

Рассмотрим взаимодействие основных блоков процессора. Команда извлекается из ОЗУ и по магистрали данных МД передается регистр команд РгК. Код команды поступает через блок адресации БА и блок управления микрокомандами БУМК, чтобы преобразовать его в первый адрес микрокоманды в запоминающем устройстве микрокоманд ЗУМК. Затем выполняется несколько микроопераций для поиска данных в ОЗУ и передачи их в микропроцессор МП, выполнения операций в арифметическо-логическом блоке, контроля переполнения и запросов на прерывание и т.д.

Выходной код с ЗУМК является микрокомандой, обычно содержащей около 40 разрядов, например 9 разрядов для определения операции арифметическо-логического блока, 8 разрядов для адресации двух исходных операндов СОЗУ; остальные разряды – для сигналов выдачи выходных результатов, управления ОЗУ, приемопередатчиками, стеком и т.д.

Наличие регистра микрокоманд РгМК дает возможность организовать конвейерную работу процессора. Пусть в регистре РгМК содержится код 1 выполняемой микрокоманды. Поле микрокоманды, управляющее последовательностью микрокоманд, анализируется блоком местного управления процессора БМУПр и направляется в виде управляющих сигналов 2 в БУМК для определения адреса следующей микрокоманды. Адрес микрокоманды в виде сигналов 3 посылается в ЗУМК и новая микрокоманда поступает на выход РгМК. Микропроцессор параллельно выполняет ранее полученную микрокоманду, поскольку на реализацию микрокоманд 1-4 требуется всего лишь один цикл работы процессора. За это время микропроцессор должен пройти состояния до 5 включительно, т.е. кроме выполнения действий внутри микропроцессора должен быть передан в регистр состояния РгС код состояния процессоров. Если он не вызывает ветвления в микрокоманде, что определяет БМУПр по сигналам 6 от регистра РгС, то начинает выполняться следующая команда, уже подготовленная в РгМК. Таким образом, наличие РгМК дает возможность извлекать следующую микрокоманду параллельно с работой микропроцессора МП, что удваивает скорость работы процессора из-за исключения последовательной работы его операционной и управляющей частей.

Типичная команда в ЭВМ имеет такую последовательность исполнения отдельных тактов в процессе интерпретации: выборка команды; дешифрирование кода операции; выборка базового адреса; формирование исполнительного адреса; выборка операнда из ОЗУ; выполнение операции над операндом и содержимым рабочего регистра или регистра результата; засылка результата на хранение в регистр результата или рабочий регистр. Во время исполнения такой команды необходимы три обращения к ОЗУ.

Высокой пропускной способности микропроцессора позволяет достичь метод перекрытия (поточный или конвейерный) путем параллельных действий над потоком команд во времени по отдельным фазам их исполнения. Выше приведенная последовательность шести тактов команды при поточном исполнении сокращает кажущееся время выполнения команд до трех тактов. При этом достигается максимально эффективное использование ресурсов ОЗУ, поскольку обращение к нему осуществляется в течение каждого такта.

Для простейшего перекрытия процесса выполнения двух команд необходим доступ к информационным полям команды, что требует отдельного регистра команд. Код команды заносится в этот регистр из буферного регистра команд ОЗУ, в который он поступил в предыдущем такте выборки команды из ОЗУ. На время выполнения микропроцессором операции необходимо хранить операнд следующей команды в буферном регистре данных. Выбранный из ОЗУ базовый адрес помещается в выходной информационный регистр. Во время исполнения данной команды надо обеспечить единичное приращение содержимого счетчика команд. Поскольку арифметическо-логическое устройство занято выполнением операций, необходимо предусмотреть отдельный сумматор или инкрементный блок для единичного увеличения кода адреса команды.

Микро-ЭВМ на основе секционного комплекта биполярных БИС, например серии К1800, может иметь 16-32 – разрядную сетку, 8-64 – уровневую приоритетную систему прерывания (цикл 100-200 нс). Это позволяет ЭВМ выполнять операции типа сложения за 100-200 нс, а операцию умножения четырехбайтовых слов – за 4-16 мкс. Система команд обеспечивает выполнение 100-150 операций, использующих 8-16 режимов адресации информации.

Дата: 2019-05-29, просмотров: 347.