После каждой операции блок сложения/вычитания генерирует сигнал переполнения MV, который подключен регистру состояния арифметики процессора ASTAT. Бит MV устанавливается в 1 если результат сложения выходит за границы регистров MR1/MR2 – 32 бита, т.е. если один из девяти старших разрядов регистра MR не 0, или все нули.

Регистр MR имеет возможность насыщения в определённом положительном или отрицательном значении, если происходит переполнение. Насыщение зависит от состояния бита MV регистра состояний арифметики ASTAT и бита MSB регистра MR2. Таблица 3.2. описывает операцию насыщения.

Таблица 3.2

| MV | MSB | Содержимое регистра MR после операции |

| 0 | 0 или 1 | Без изменений |

| 1 | 0 | 00000000 0111111111111111 1111111111111111 (положит.) |

| 1 | 1 | 11111111 1000000000000000 0000000000000000 (отрицат.) |

Насыщение в МАС является скорее командой, чем режимом, как в ALU. Она используется при завершении последовательности умножений с накоплением, таким образом, чтобы промежуточные переполнения не привели сумматор к насыщению.

Переполнение больше MSB недопустимо. В обратном случае знаковый разряд будет потерян и насыщение не будет правильным. Однако, чтобы достигнуть этого состояния требуется 255 переполнений.

Округление

Сумматор может округлять 40-разрядный результат до 15-16 разряда. Округление можно отнести к системе команд микропроцессора. Округленный результат направляется либо в MR, либо в регистр обратной связи MF. Когда для вывода используется MF, в него записывается 16-разрядный округленный результат. Аналогично, если для вывода выбран MR, то в MR1 записываются 16 разрядов округленного результата, а в MR2 – эффект округления, таким образом получается 24-разрядный округленный результат.

Сумматор использует несмещенную схему округления. Стандартный метод смещенного округления состоит в записи 1 в 15-ю разрядную позицию. Этот метод вызывает ряд положительных смещений, начиная с середины (когда MR=0х8000), округляя результат вверх. Сумматор же устраняет это смещение, устанавливая 16 бит в 0, когда значение регистра MR достигает середины. При этом четные значения MR1 округляются вниз, а нечетные вверх. Таким образом получается однородная последовательность смещений.

Пример типичной операции округления:

MR2 MR1 MR0

Неокругленное значение : xxxxxxxx xxxxxxxx00100101 1xxxxxxxxxxxxxxx

Бит 15 = 1

Прибавляем 1 к 15 разряду и смещаем 1

Округленное значение : xxxxxxxx xxxxxxxx00100110 0xxxxxxxxxxxxxxx

MR2 MR1 MR0

Неокругленное значение : xxxxxxxx xxxxxxxx01100110 1000000000000000

Бит 15 = 1 и биты 0-14 = 0

Прибавляем 1 к разряду 15 и сдвигаем 1

xxxxxxxx xxxxxxxx01100111 0000000000000000

Сейчас бит 16 = 1, устанавливаем его в 0

Округленно значение : xxxxxxxx xxxxxxxx01100110 0000000000000000

В последнем случае 16 бит устанавливается в 0. Этот алгоритм применяется на каждой операции округления.

Смещенное округление

Режим смещенного округления возможен в процессорах ADSP-217x, ADSP-218x, и ADSP-21msp58/59. Этот режим выбирается путем установки бита BIARND регистра управления SPORT0. Если BIARND=0, то используется операция несмещенного округления, если BIARND=1, то смещенного.

Пример:

MR перед RND Смещенный результат RND Несмещенный результат RND

00-0000-8000 00-0001-8000 00-0000-8000

00-0001-8000 00-0002-8000 00-0002-8000

00-0000-8001 00-0001-8001 00-0001-8001

00-0001-8001 00-0002-8001 00-0002-8001

00-0000-7FFF 00-0000-7FFF 00-0000-7FFF

00-0001-7FFF 00-0001-7FFF 00-0001-7FFF

Этот режим эффективен только, в том случае, когда значение регистра MR0 больше 0х8000. Во всех других случаях работают обычные операции округления. Этот режим позволяет более эффективно реализовывать алгоритмы, использующие смещенное округление, например, подпрограммы речевого сжатия GSM.

BARREL SHIFTER

Shifter предоставляет полный набор сдвиговых функций для 16- и 32-разрядных операндов. Это арифметические сдвиги, логические сдвиги и нормализация. Так же shifter выполняет сортировку. Эти базисные функции могут быть объединены, чтобы реализовать работу с числами любого формата, в том числе с плавающей точкой.

Описание блок схемы

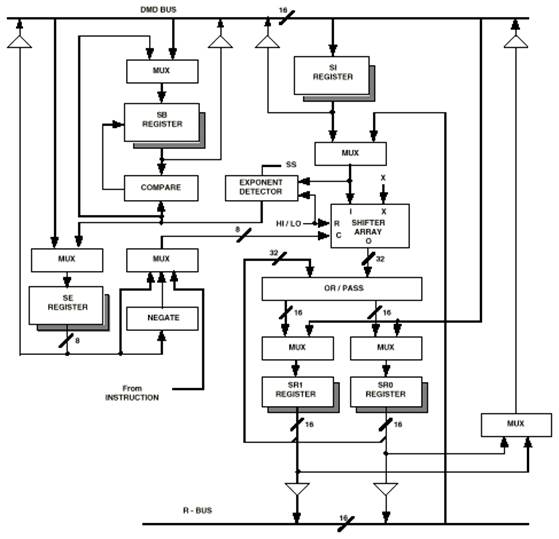

Рисунок 4.1 иллюстрирует блок схему модуля сдвига. Shifter может быть разделен на следующие части: массив сдвига, логика OR/PASS, детектор порядка и логика сравнения порядка.

|

Массив сдвига принимает 16-разрядные данные и в одном цикле может поместить их в любой позиции 32-разрядного поля вывода. Это дает 49 возможных размещений в поле вывода. Размещение 16-ти входных разрядов определяется кодом управления C и сигналом ссылки HI/LO.

Массив сдвига и связная логика OR/PASS окружены набором регистров. Входной регистр Shifter (SI) содержит данные для массива сдвига и детектора порядка. SI-16-разрядный, записывается и читается с DMD-шины. В качестве входных регистров для массива сдвига и детектора порядка могут служить AR, SR или MR, подключенные через R-шину. Выходной 32-разрядный регистр SR разделен на две части по 16 разрядов: SR0 и SR1. Они могут быть загружены с DMD шины и выведены на R- или DMD-шину. Также SR подключен к блоку OR/PASS логики для проведения сдвигов двойной точности.

Дата: 2019-05-29, просмотров: 326.