Проектування типових функціональних вузлів комп'ютера містить у собі такі етапи:

1. Змістовна постановка задачі. Указують тип і розрядність проектованого вузла, особливості його зв'язків з іншими вузлами, тип схемної логіки, вимоги до швидкодії споживаної потужності.

2. Аналіз розмірності (розрядності) задачі. На основі аналізу розмірності задачі приймають рішення про проектування вузла як цілісної системи або, у випадку великої розмірності, розбивають його на модульно-розрядні частини. Наприклад, синтезується однорозрядний суматор і потім за допомогою ланцюгів перенесення будується регулярна структура багаторозрядного суматора.

3. Формалізоване задання алгоритмів роботи вузла. Логіку функціонування вузла задають таблицями істинності чи мікрооперацій, графом, картами Карно.

4. Подання алгоритмів роботи вузла аналітичними виразами. Вигляд логічних рівнянь залежить від способу формалізованого задання роботи вузла. У разі використання таблиць істинності логічні рівняння записуються в канонічних формах - досконалих диз'юнктивних (ДДНФ) чи кон'юнктивних (ДКНФ) формах. Якщо робота вузла описується таблицею мікрооперацій, то в логічні рівняння як змінні включаються також і керуючі сигнали.

5. Мінімізація одержаних логічних рівнянь, поданих у вигляді ДДНФ. Зручно виконувати за допомогою карт Карно чи діаграм Вейча (якщо число змінних не більше шести). Якщо число змінних більше шести, то використовують машинні способи мінімізації. Мінімізовані форми логічних рівнянь забезпечують побудову схем меншої вартості.

6. Перетворення мінімальних форм рівнянь до вигляду, зручного для реалізації в заданому елементному базисі. Проектування вузлів часто здійснюють на універсальних логічних елементах НЕ І або НЕ ЧИ. Для переходу до такого елементного базису виконують перетворення мінімальних диз'юнктивних або кон'юнктивних нормальних форм за допомогою правил подвійної інверсії з наступним застосуванням правил де Моргана.

Синтез заданого функціонального вузла

Для правильної роботи арифметико-логічного пристрою комп'ютера на виконання операції додавання чи віднімання в доповняльному коді нам потрібно синтезувати такі основні функціоналні вузли комп'ютера: лінійний дешифратор на три входи х1-х3 і вісім прямих виводів F0 - F7; схема контролю за парністю; схема перетворювача прямого коду в доповняльний.

Проектування лінійного дешифратора на три входи х1-х3 і вісім прямих виводів F0 - F7.

Логіка функціонування дешифратора задається таблицею іс-тинності (табл. 1.1.).

Таблиця 1 - Таблиця істинності лінійного дешифратора «3>8»

| Х3 | Х2 | Х1 | F0 | F1 | F2 | F3 | F4 | F5 | F6 | F7 | |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

На підставі даних табл. 1. записується система логічних рівнянь для прямих виходів лінійного дешифратора у ДДНФ:

F0?= Х 3 Х 2 Х 1; F1?= Х 3 Х 2 Х 1; F2?= Х 3 Х 2 Х 1; F3?= Х 3 Х 2 Х 1;

F4?= Х 3 Х 2 Х 1; F5?= Х 3 Х 2 Х 1; F6?= Х 3 Х 2 Х 1; F7?= Х 3 Х 2 Х 1.

Згідно із системою для побудови лінійного дешифратора «3>8» необхідно використати 8 тривходових логічних елементів І та три елементи НЕ

Типи логіки

Розвиток мікроелектроніки сприяло розвитку малогабаритних, високонадійних і економічних пристроїв на підставі цифрових ІМС Вимоги збільшення швидкодії та зменшення споживаної потужності обчислювальних пристроїв привели до створення серій цифрових мікросхем. За час розвитку цифрових мікросхем базові типи логіки розвивалися в наступній послідовності:

1. діод-транзисторна логіка (ДТЛ);

2. транзисторних-транзисторна логіка (ТТЛ);

3. емітерний-пов'язана логіка (ЕСЛ);

4. транзисторних-транзисторна логіка з діодами Шотткі;

5. інтегрально-инжекционная логіка (ІІЛ);

На даний момент найбільшого поширення набули схеми із застосуванням елементів ТТЛ. Це викликано тим, що ІМС на елементах ТТЛ при відносно невеликій споживаної потужності мають досить високу швидкодію. Використання в ІМС на елементах ТТЛ переходів Шотки ще більш збільшило швидкодію схем і дало можливість створювати малопотужні швидкодіючі ІМС.

Для курсового проекту є мікросхема серії К1533

Цей комплекс мікросхем виконаний по ТТЛ - технології, характеризуються архітектурним єдністю, яке забезпечується автономністю і функціональної закінченістю окремих мікросхем, уніфікацією їх інтерфейсу, можливість програмування мікросхем, їх логічної і електричної сумісністю. Низька швидкодія і низьке споживання - SN74ALS забезпечують широке застосування при створенні засобів обчислювальної техніки.

Ці мікросхеми в робочому стані матимуть температуру свого корпусу -50º, а можуть витримувати температуру до -70º, тому ці мікросхеми найбільш зручні для застосування в бортовій апаратурі на високою висоті при низьких температурах.

Вибираемо мікросхему з серії К1533

Таблиці

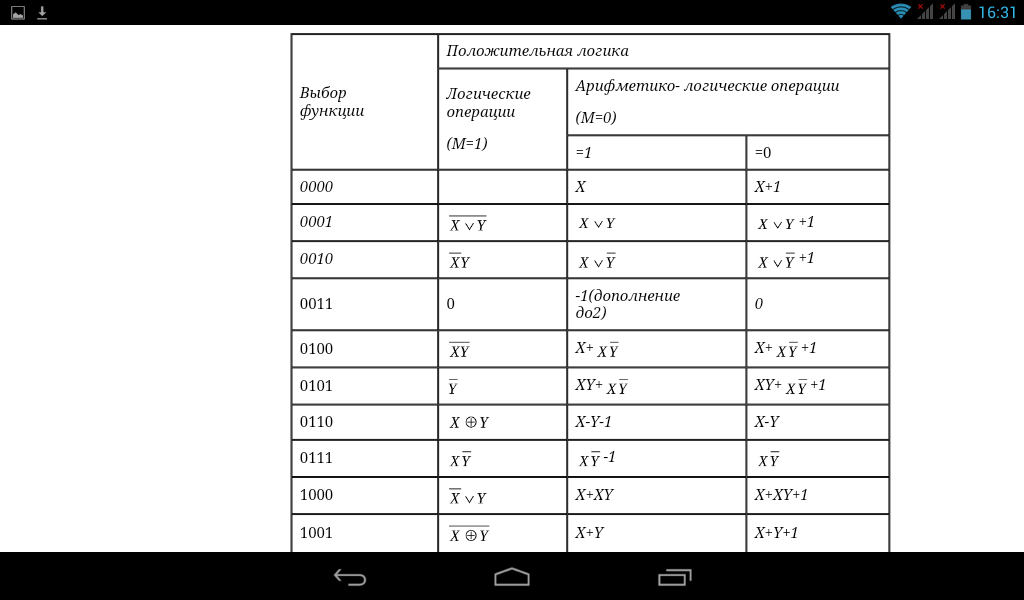

Таблиця 1.Операції виконувані АЛУ

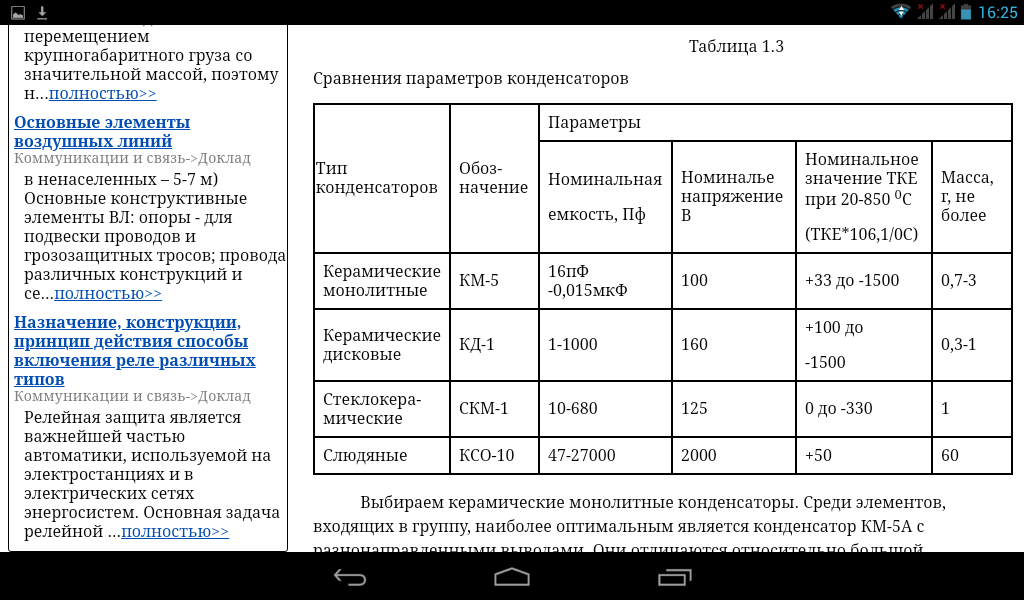

Так як в даному модулі конденсатори необхідні для блокування низькочастотних перешкод, що надходять на схему по шині харчування, і як такі не беруть участь в роботі мультиплексора, то доцільно використовувати низьковольтні конденсатори. Результати порівняння параметрів конденсаторів приведені в таблиці 1.3.

Таблиця.2

Порівняння параметрів конденсаторів

Розрахункова частина

Дата: 2019-02-02, просмотров: 443.