Программно управляемый обмен данными предполагает передачу данных из ВУ в аккумулятор, а затем в память или наоборот, из памяти в аккумулятор, а потом в выходной регистр. Однако, программно управляемая пересылка данных – это медленный процесс. При пересылке больших массивов данных это обстоятельство вызывает определенные проблемы. Ранее рассмотренные методы обмена данными относились к передачам между ВУ и МП.

Прямой доступ к памяти (ПДП) – это способ организации быстрой пересылки данных при обмене информацией между памятью и ВУ (внешними устройствами).

Если требуется осуществить обмен между ВУ и памятью, то нет необходимости пересылать данные через МП. В этом режиме обмен данными между ВУ и ОЗУ происходит без участия МП. Обычно между памятью и ВУ обмен данными заключается в пересылке массивов информации. Построение канала ПДП является альтернативой программному обмену. Обменом в режиме ПДП управляет не программа, выполняемая МП, а электронная схема Б И С, внешняя по отношению к МП.

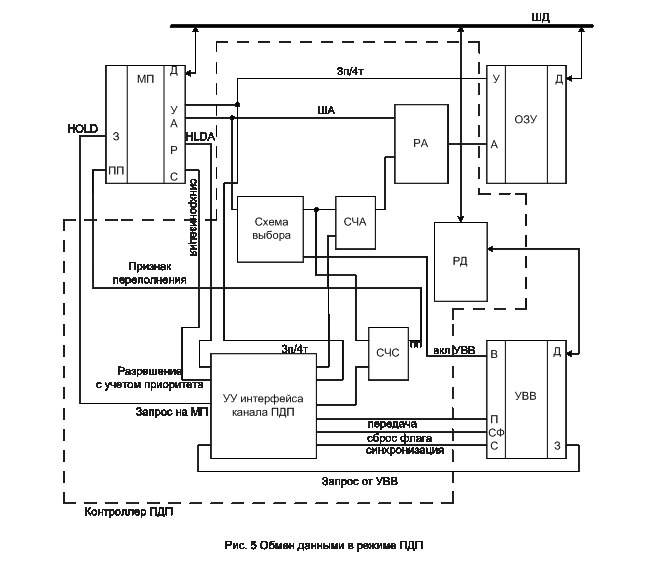

Аппаратные средства реализации канала ПДП называются контроллером ПДП (КПДП). Схема, управляющая обменом в режиме ПДП, размещается в специальном контроллере, который называется контроллером прямого доступа к памяти.

Для реализации режима прямого доступа к памяти необходимо обеспечить непосредственную связь контроллера ПДП и памяти микро-ЭВМ. Для этой цели можно было бы использовать специально выделенные ША и ШД, связывающие контроллер ПДП и ОЗУ. Однако такое решение значительно усложнит микро-ЭВМ. В целях сокращения количества линий в шинах микро-ЭВМ контроллер ПДП подключается к ОЗУ посредством шин адреса и данных системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса МП и контроллером ПДП.

В МП с возможностью ПДП для их принудительного отключения от ША и ШД имеются специальные выводы HOLD и HLDA. Запрос на начало режима прямого доступа к памяти подается контроллером ПДП на вход HOLD (захват) МП БИС. МП, получив этот сигнал, приостанавливает выполнение текущей команды, не дожидаясь ее завершения, выставляет на свой выход HLDA управляющий сигнал предоставления ПДП и отключается от шин адреса и данных. С этого момента все шины микро-ЭВМ управляются контроллером ПДП. МП во время передачи информации по каналу ПДП переводит схемы управления магистралями в высокоомное состояние и тем самым изолируется от остальной части системы. Состояние внутренних регистров замораживается, т.е. МП в режиме ожидания сохраняет то информационное состояние, которое было в нем к моменту удовлетворения запроса канала ПДП.

Интерфейс канала ПДП по сложности превосходит другие типы интерфейсов. Хотя его структура может быть упрощена за счет программной реализации части функций, это не представляется целесообразным, так как основная цель использование режима ПДП – обеспечение высокой скорости передачи данных. Передача данных в режиме ПДП имеет приоритет перед другими видами обмена. Режим ПДП всегда требует предварительной подготовки: для каждого ВУ необходимо выделить область памяти, используемую при обмене, и указать ее размер (количество записываемых в память или читаемых из памяти байт информации). Поэтому любой КПДП имеет в своем составе регистр адреса и счетчик байт. На рисунке представлена схема реализации канала ПДП.

УВВ вырабатывает сигнал запроса на цикл обращения к ОЗУ, который через УУ интерфейса канала ПДП поступает на МП (вход HOLD ). МП отвечает сигналом разрешения на захват цикла с учетом приоритета УВВ (выход HLDA ). УУ сигналом C Ф (сброс флага) сбрасывает в нуль триггер ВУ, тем самым сообщая ему о начале цикла ПДП. После этого в УУ устанавливается единичное состояние триггер активности, что приводит к передаче из МП в регистр адреса РА адреса первой ячейки памяти ОЗУ передаваемого массива данных. Далее сигналом П (Передача) инициируется передача данных между УВВ и ОЗУ. Обмен между ОЗУ и УВВ происходит через буферный регистр данных РД. УВВ предоставляется только один цикл работы микро-ЭВМ. Поэтому после записи в ОЗУ или чтения одного байта данных триггер активности УУ сбрасывается в «0», а МП возобновляет выполнение основной программы. Когда УВВ подготовится к следующему обмену, оно вновь установит в «1» свой флаговый триггер, что приведет к посылке в УУ нового запроса на доступ к памяти. Предварительно в РА должен быть установлен новый адрес ячейки ОЗУ и посчитано число уже переданных байт данных. Для выполнения этих функций в контроллер ПДП введены два счетчика: счетчик слов (СЧС) и счетчик адреса (СЧА). СЧС изначально загружается числом передаваемых байт (кодом длины массива), а СУА – начальным адресом ОЗУ. В процессе обмена после каждого обращения к ОЗУ производится инкремент адреса в СЧА и декремент счетчика байт СЧС. Переполнение счетчика слов СЧС является признаком конца массива. Поэтому признак переполнения (ПП) останавливает передачу данных, КПДП прекращает формирование сигналов запроса ПДП и этот режим заканчивается .

Запоминающие устройства

Классификация ЗУ .

Дата: 2018-12-28, просмотров: 788.