В основе устройства управления МП используется цифровой автомат. Любая современная микропроцессорная система поддерживает три основных режима обмена по магистрали:

- программный обмен информацией;

- обмен с использованием прерываний (Interrupts— сигнал от программного или аппаратного обеспечения, сообщающий процессору о наступлении какого-либо события, требующего немедленного внимания. Прерывание извещает процессор о наступлении высокоприоритетного события, требующего прерывания текущего кода, выполняемого процессором.;

- обмен с использованием прямого доступа к памяти (ПДП, DMA — Direct Memory Access).

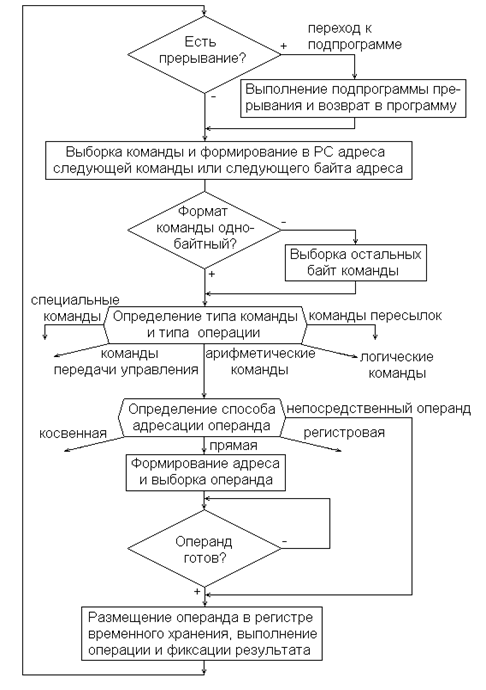

Примерная схема алгоритма функционирования управляющего автомата в течение рабочего цикла выполнения команды приведена на рисунке ниже.

Рабочий цикл выполнения команды МП

Выполнение рабочего цикла команды начинается с опроса триггера прерывания. Если запрос прерывания поступил и прерывания разрешены (командой EI), то автомат формирует машинный цикл обработки прерывания, в котором управление передается подпрограмме обработки прерывания, и она выполняется. При отсутствии прерывания управляющий автомат формирует цикл выборки команды из памяти и формирует адрес следующей команды.

Далее управляющий автомат дешифрирует код операции в команде и генерирует соответствующую коду операции серию управляющих сигналов, обеспечивающую выполнение в МП заданной операции.

Устройство управления МП в зависимости от кода текущей команды, состояния своего управляющего автомата, а также в зависимости от значений сигналов оповещения с шины управления МПС вырабатывает последовательности сигналов, реализующие процедуры системного обмена информацией.

В МП управляющий автомат в зависимости от сложности команды выполняет цикл команды за несколько (1-5) внутренних машинных циклов. Один машинный цикл требуется МП для одного обращения к памяти или УВВ. Например, машинный цикл МП ВМ80 (функциональный аналог микропроцессора Intel i8080A ) может состоят из 3-5 тактов. Тактирование МП осуществляется от внешнего генератора сигналами F1, F2 .

В стандартном машинном цикле может быть от трех до пяти состояний автомата управления.

Микропроцессор приступает к анализу запросов на прерывание только после окончания выполнения текущей команды.

Из состояния останова МП может быть выведен сигналом прерывания INT или сигналом установки в исходное состояние Reset.

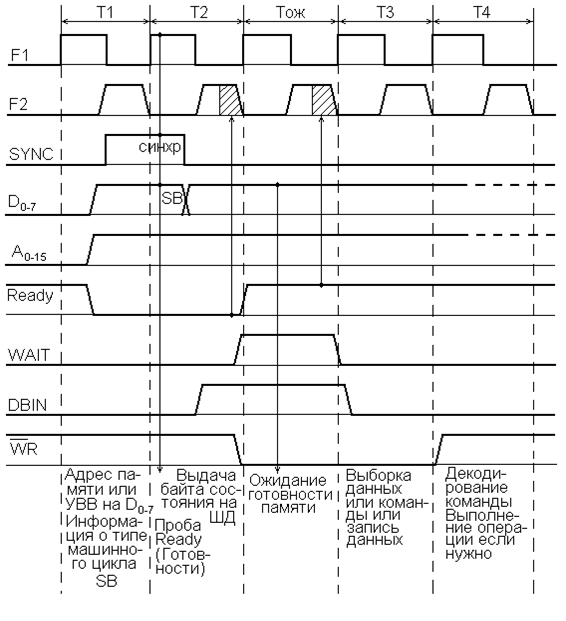

Временная диаграмма выполнения основного цикла команды МП

Временная диаграмма определяет основной цикл команды МП. В первом такте синхронизации Т1 МП выставляет на шине адреса код адреса А0-15 очередной команды. Одновременно на линии синхронизации SYNC появляется единичный сигнал, который идентифицирует информацию на шине данных D0-7 как байт состояния SB процессора и загружает его в регистр системного контроллера ( например К580ВК28 ).

Сигнал SYNC также свидетельствует о начале машинного цикла. По окончании сигнала SYNC буферная схема шины данных, расположенная в системном контроллере, переводит шину данных D0-7 в режим ввода, о чем свидетельствует единичный сигнал на линии DBIN шины управления.

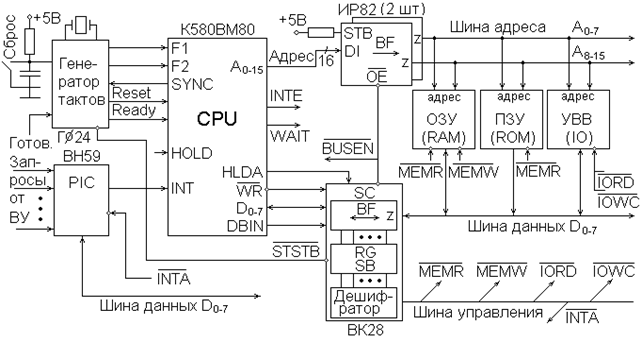

Структурная схема микропроцессора

В такте Т2 МП осуществляет проверку готовности внешнего устройства (или памяти). Если внешнее устройство не формирует сигнал Готов (высокий уровень), то автомат управления МП переходит в состояние ожидания. В этом состоянии МП будет находиться до тех пор, пока на линии Ready не появится единичный сигнал, который будет свидетельствовать о том, что память или ВУ готовы к обмену. На временных диаграммах приведен вариант отсутствия готовности в течение одного такта и МП сформировал один такт ожидания Тож, в котором обнаружил единичный сигнал готовности Ready и перешел к рабочему такту Т3. В такте Т3 МП производит чтение или запись слова в память. Такты Т4 и Т5 отводятся для выполнения операции, заданной кодом операции команды. Выполнение некоторых сложных команд требует неоднократного прохода по циклу состояний автомата управления от Т1 до Т5.

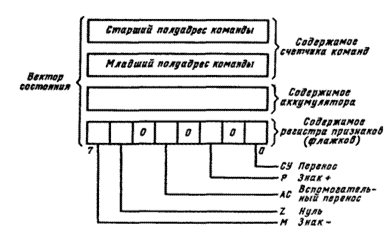

Слово состояния процессора

При выполнении процессором программы после каждого рабочего такта, а тем более в результате завершения выполнения очередной команды, изменяется содержимое регистров, счетчиков, состояния отдельных управляющих триггеров. Можно говорить, что изменяется состояние процессора, или, употребляя другую терминологию, состояние программы. Информация о состоянии процессора (программы) лежит в основе многих процедур управления вычислительным процессом, например при анализе ситуаций при отказах и сбоях, при возобновлении выполнения программы после перерывов, вызванных отказами, сбоями, прерываниями, для фиксации состояния процессора (программы) в момент перехода в мультипрограммном режиме от обработки данной программы к другой и т. п.. Состоянием процессора (программы) после данного такта или после выполнения данной команды, строго говоря, следует считать совокупность состояний в соответствующий момент времени всех запоминающих элементов устройства — триггеров, регистров, ячеек памяти. Однако не вся эта информация исчезает или искажается при переходе к очередной команде или другой программе. Поэтому из всего многообразия информации о состоянии процессора (программы) отбираются наиболее существенные ее элементы, как правило, подверженные изменениям при переходе к другой команде или программе.

Совокупность значений этих информационных элементов получила название вектора состояния или слова состояния процессора (программы).

Слово состояния процессора (на примере МП К580)

Вектор состояния в каждый момент времени должен содержать информацию, достаточную для продолжения выполнения программы или повторного пуска программы с точки, соответствующей моменту формирования данного вектора состояния. При этом предполагается, что остальная информация, характеризующая состояние процессора, например содержимое регистров, или сохраняется, или может быть восстановлена программным путем по копии, сохраненной в памяти. Вектор состояния формируется в соответствующем регистре (регистрах) процессора, претерпевая изменения после выполнения каждой команды. Наборы информационных элементов, образующих векторы состояния, отличаются у ЭВМ разных типов. Наиболее просто он выглядит у микропроцессоров. Например, вектор состояния микропроцессора К580, включает в себя содержимое 16-разрядного счетчика команд (адрес очередной команды); содержимое 8-разрядного регистра признаков, называемое в документации на этот микропроцессор словом состояния процессора, и содержимое 8-разрядного аккумулятора АЛУ. Использование слова (вектора) состояния — распространенный прием построения управления устройствами вычислительной техники.

Для нормального функционирования МПС недостаточно управляющих сигналов, формируемых МП на собственных выводах т.к., нельзя отличить циклы обращения к памяти от циклов обращения ввода-вывода. Расширение числа управляющих сигналов достигается с помощью специального 8-разрядного кода BS (байта состояния), который МП выдает через шину данных в первом такте Т1 каждого машинного цикла. Байт состояния BS содержит информацию о текущем машинном цикле. Таким образом, в каждом машинном цикле МП формирует код типа текущего машинного цикла, который далее декодируется в системном контроллере. В результате декодирования кода типа машинного цикла формируется расширенный набор сигналов шины управления для управления памятью, устройствами ввода-вывода и прерываниями. Всего 11 типов машинных циклов:

1. FETCH Цикл М1 приема первого байта команды в

регистр IR .

2. MEMORY_READ Цикл чтения данных из памяти по адресу,

определяемому PC, BC, DE, HL.

3. MEMORY_WRITE Цикл записи данных в память по адресу,

определяемому BC, DE, HL, SP.

4. STACK-READ Цикл чтения из стека, чтение памяти по адресу, определяемому SP.

5. STACK-WRITE Цикл записи в стек, запись в память по адресу,

определяемому SP.

6. INPUT Цикл ввода данных из порта в аккумулятор А.

7. OUTPUT Цикл вывода данных из аккумулятора в порт.

8. INTERRUPT-M1 Первый цикл подтверждения прерывания .

9. HALT Цикл останова.

10. HALT-INTERRUPT Первый цикл подтверждения прерываний в

состоянии останова.

11. INTERRUPT Второй и третий циклы подтверждения прерывания.

Назначение линий управления

F1 и F2 Это входные линии приема взаимно противофазных сигналов тактирования МП. Поступают с генератора тактовых импульсов (рис.2.19).

SYNC Выходная линия, на которую микропроцессор в начале каждого машинного цикла формирует сигнал синхронизации устройств, входящих в систему.

Ready Входная линия приема МП сигнала от ВУ, информирующих о готовности принять или выдать данные (высоким уровнем).

WAIT Выходная линия, на которую МП выставляет сигнал ожидания (высокий уровень), если в такте Т2 отсутствует высокий уровень на линии Ready.

Reset По этой линии поступает сигнал установки МП в исходное состояние. При этом в программный счетчик РС загружается стартовый адрес РС=0000h, с которого начинается пусковая программа. В регистр команд IR записывается код пустой команды NOP, т.е. IR=00h. Внутренние триггеры “разрешение прерывания” и “подтверждение захвата шины” устанавливаются в нулевое состояние. Состояние РОН и регистра признаков F по сигналу Reset не изменяется.

INT Линия приема сигнала запроса на прерывание от ВУ. МП анализирует состояние этой линии в конце текущей команды или в состояние “Останов”. И если внутренний триггер “разрешения прерываний” установлен в состояние “разрешено” (командой EI), то МП формирует машинные циклы обработки прерывания, выставляя на шину данных байт состояния SB, на основе которого системный контроллер вырабатывает сигналы INTA #.

INTE Выходная линия, на которую МП формирует сигнал

“разрешение прерывания”.

HOLD Входная линия приема сигнала запроса шин, поступающая от ВУ.

HLDA Выходная линия, на которую микропроцессор выставляет сигнал “подтверждение захвата шин” в ответ на сигнал HOLD. При этом буферы на шинах адреса и данных устанавливает в Z-состояние.

DBIN Выходная линия, на которую МП формирует сигнал высокого

уровня при выполнении команд чтения памяти или УВВ.

WR# Выходная линия. При выполнении команд записи в память или

УВВ МП выставляет сигнал низкого уровня.

Генератор тактовых импульсов формирует две взаимно противофазные импульсные последовательности F1 и F2. Микропроцессор воспринимает эти тактирующие сигналы, пересчитывает их с коэффициентом пересчета 3-5. Величина коэффициента пересчета определяется типом выполняемой в данный момент команды. В начале каждого машинного цикла микропроцессор формирует сигнал синхронизации (SYNC), который поступает на генератор тактовых импульсов. В генераторе тактовых импульсов с приходом сигнала SYNC формируется сигнал STSTB#, служащий для стробирования записи байта состояния SB процессора в регистр системного контроллера. Таким образом, в каждом машинном цикле МП формирует код типа текущего машинного цикла, который далее декодируется в системном контроллере. В результате декодирования кода типа машинного цикла формируется расширенный набор сигналов шины управления для управления памятью, устройствами ввода-вывода и прерываниями. Все сигналы имеют активным низкий уровень:

MEMRD# строб-сигнал чтения памяти.

MEMWR# строб-сигнал записи в память.

IORD# строб-сигнал чтения УВВ (портов).

IOWRC# строб-сигнал записи в УВВ (порты).

INTA# сигнал подтверждения прерывания. Используется для

стробирования чтения адреса подпрограммы обработки прерывания, например из контроллера прерывания КР580ВН59.

Дата: 2018-12-28, просмотров: 783.